Menu

En este apartado presento las distintas líneas de investigación en las que colaboro como parte de mi trabajo en la Universidad de Zaragoza. Estas líneas de investigación son las siguientes:

- Sistemas Heterogéneos Balanceo de carga entre dispositivos de computación. Paradigmas y lenguajes de programación: efectividad y programabilidad. Optimización de aplicaciones para altas prestaciones o eficiencia energética.

- microArquitectura Diseños para mejorar el rendimento y aumentar la eficiencia energética. Técnicas para reducir el impacto del envejecimiento hardware. Modelado analítico de hardware.

- Seguridad en el Hardware Trusted execution environments. Ataques especulativos a la microarquitectura.

- Sistemas de Tiempo Real Cálculo del tiempo de ejecución de pero caso. Análisis de planificabilidad de tareas. Análisis de código estático para generación automática de restricciones para el cálculo del WCET.

A continuación listo algunos de los resultados que he publicado como parte de mi labor investigadora:

-

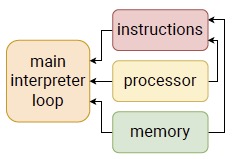

peRISCVcope: A Tiny Teaching-Oriented RISC-V Interpreter

D Suárez Gracia, A Valero, R Gran Tejero, M Villarroya, V Viñals

37th Conference on Design of Circuits and Integrated Circuits (DCIS). 2022

[DOI] [pdf] -

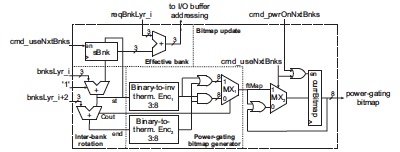

Gated-CNN: Combating NBTI and HCI aging effects in on-chip activation memories of Convolutional Neural Network accelerators

N Landeros Muñoz, A Valero, R Gran Tejero, D Zoni

Journal of Systems Architecture. 2022

[DOI] [pdf] -

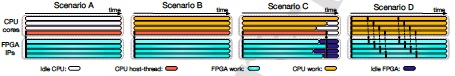

Lightweight asynchronous scheduling in heterogeneous reconfigurable systems

A Rodríguez, A Navarro, K Nikov, J Nunez-Yanez, R Gran Tejero, D Suárez Gracia, R Asenjo

Journal of Systems Architecture. 2022

[DOI] [pdf] -

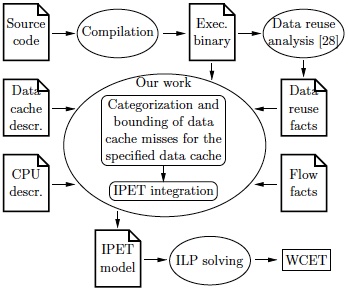

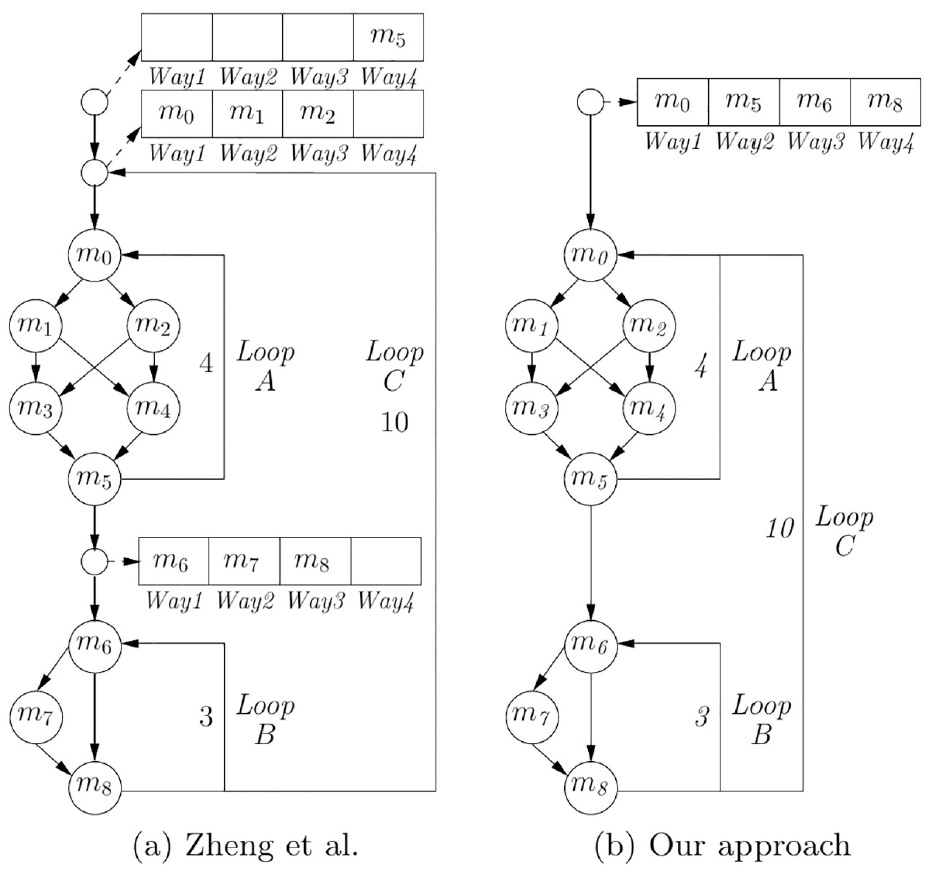

A Generic framework to integrate data caches in the WCET analysis of real-time systems

J Segarra, R Gran Tejero, V Viñals Yúfera

Journal of Systems Architecture. 2021

[DOI] [pdf]

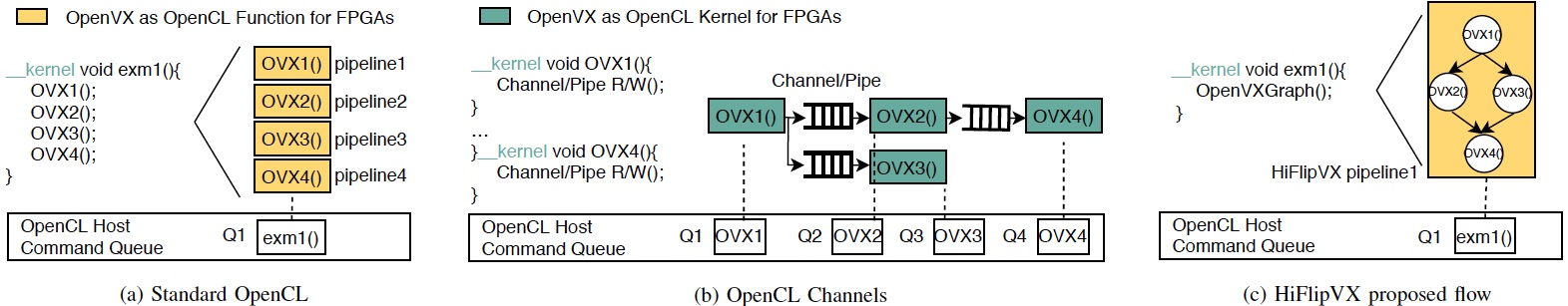

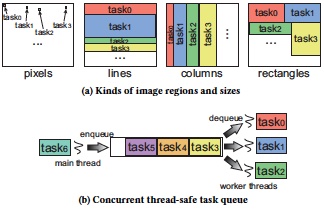

A Cross-Platform OpenVX Library for FPGA Accelerators

MA Dávila-Guzmán, R Gran Tejero, M Villarroya-Gaudó, DS Gracia, L Kalms, D Göhringer

Journal of Systems Architecture (JSA). 2021. An extension of PDP 2021

[DOI] [pdf]-

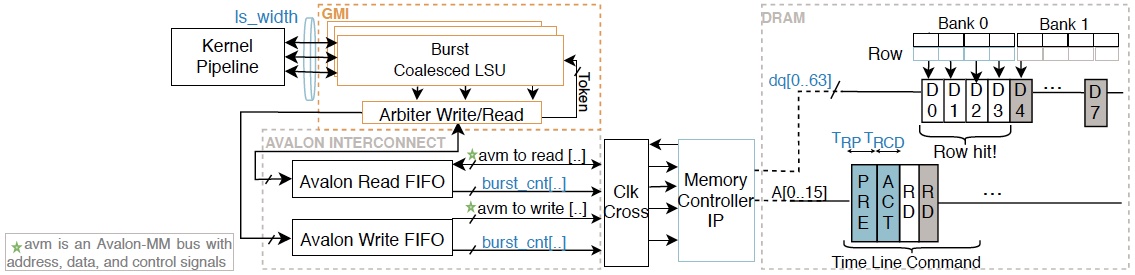

Analytical Model for Memory-Centric High Level Synthesis-Generated Applications

MA Davila Guzman, R Gran Tejero, M Villarroya-Gaudo, D Suarez-Gracia

IEEE Transactions on Computers. 2021

[DOI] [pdf]

A learning experience toward the understanding of abstraction-level interactions in parallel applications

A Valero, R Gran-Tejero, D Suárez-Gracia, EA Georgescu, J Ezpeleta, Pedro Álvarez, Adolfo Muóz, Luis M. Ramos, Pablo Ibáñez

Journal of Parallel and Distributed Computing. 2021

[DOI] [pdf]

RRCD: Redirección de Registros Basada en Compresión de Datos para Tolerar Fallos Permanentes en una GPU

Y Toca-Díaz, A Valero, R Gran-Tejero, D Suárez-Gracia

arXiv preprint arXiv:2105.03859. 2021

[DOI] [pdf]

A Cross-Platform OpenVX Library for FPGA Accelerators

MA Dávila-Guzmán, RG Tejero, M Villarroya-Gaudó, DS Gracia, L Kalms, D Göhringer

29th Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP). 2021

[DOI] [pdf]

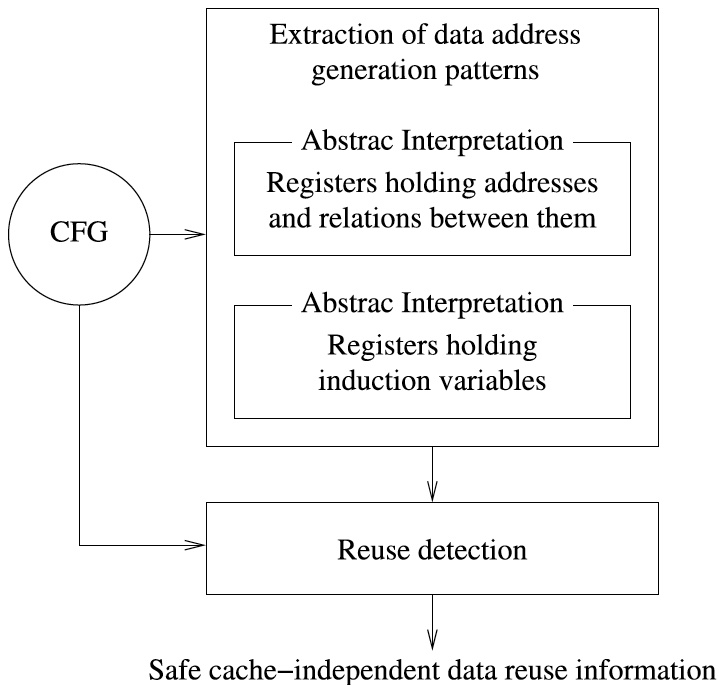

Automatic Safe Data Reuse Detection for the WCET Analysis of Systems With Data Caches

J Segarra, J Cortadella, RG Tejero, V Viñals-Yúfera

IEEE access 8, 192379-192392. 2020

[DOI] [pdf]

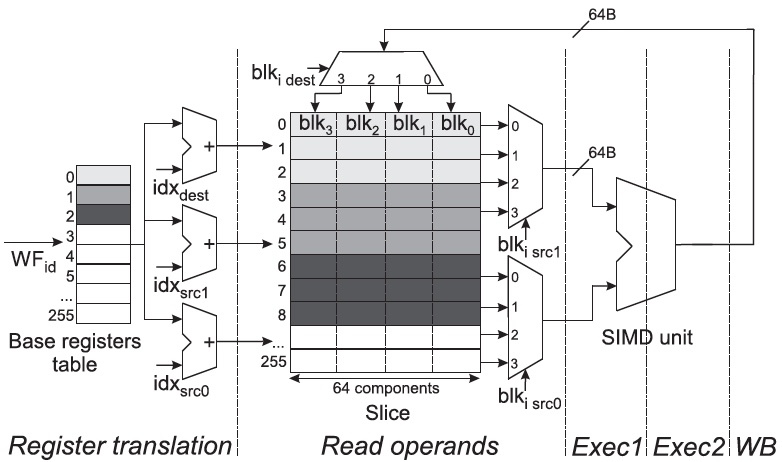

DC-Patch: A Microarchitectural Fault Patching Technique for GPU Register Files

A Valero, D Suárez-Gracia, R Gran-Tejero

IEEE Access 8, 173276-173288. 2020

[DOI] [pdf]

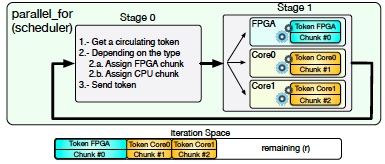

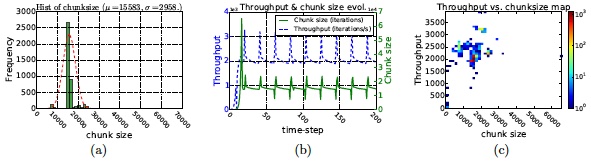

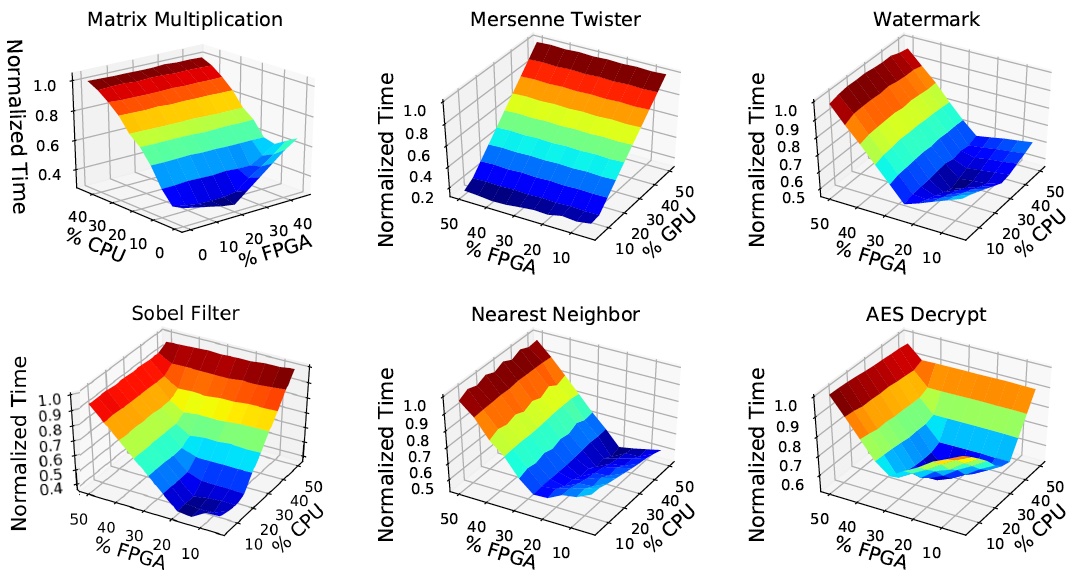

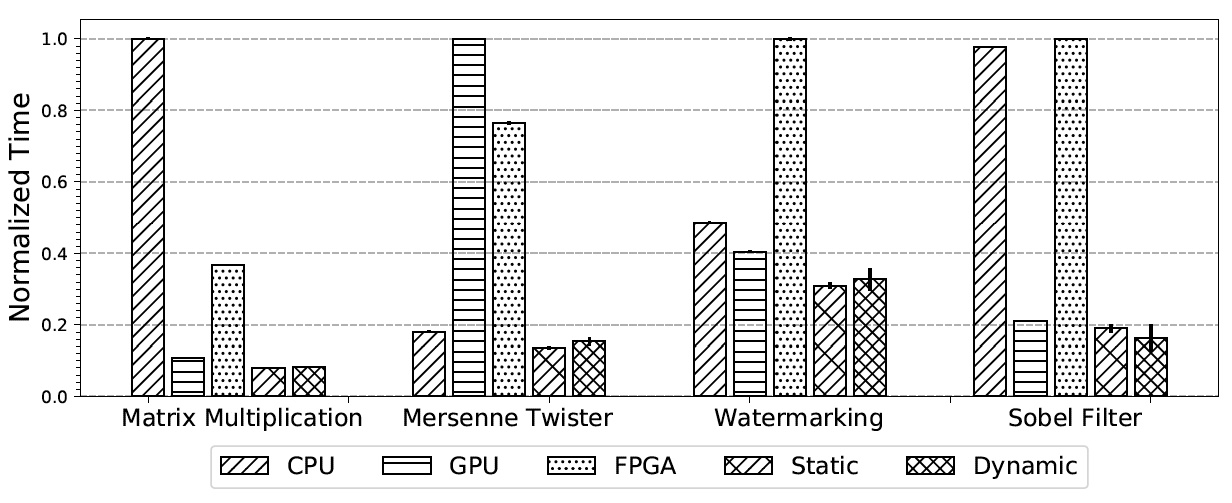

Parallel multiprocessing and scheduling on the heterogeneous Xeon+ FPGA platform

A Rodríguez, A Navarro, R Asenjo, F Corbera, R Gran, D Suárez, J Núñez-Yañez

Journal of Supercomputing 76, 4645–4665. 2020

[DOI] [pdf]

An Analytical Model of Memory-Bound Applications Compiled with High Level Synthesis

MA Dávila-Guzmán, R Gran Tejero, M Villarroya-Gaudó, DS Gracia

2020 IEEE 28th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). 2020

[DOI] [pdf]

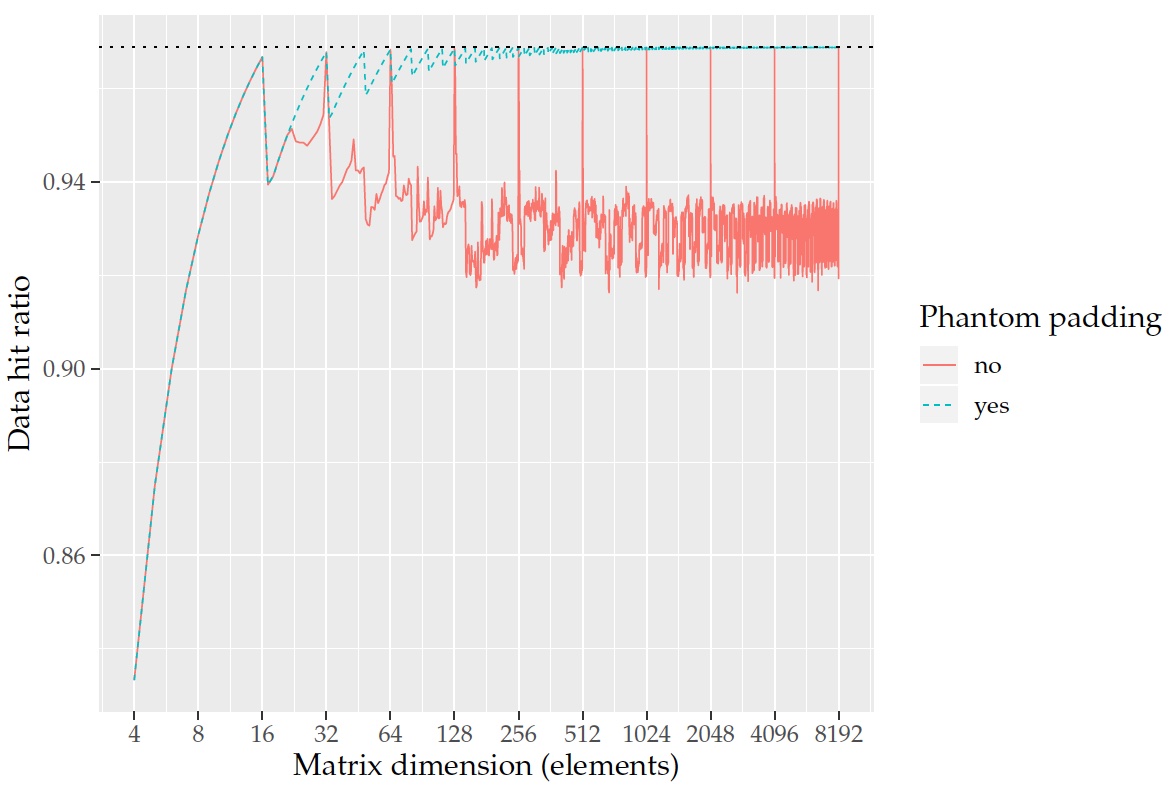

Reducing the WCET and analysis time of systems with simple lockable instruction caches

A Pedro-Zapater, J Segarra, R Gran Tejero, V Viñals, C Rodríguez

PloS one 15 (3), e0229980. 2020

[DOI] [pdf]

Ideal and Predictable Hit Ratio for Matrix Transposition in Data Caches

A Pedro-Zapater, C Rodríguez, J Segarra, R Gran Tejero, V Viñals-Yúfera

Mathematics 8 (2), 184. 2020

[DOI] [pdf]

Exploring heterogeneous scheduling for edge computing with CPU and FPGA MPSoCs

A Rodríguez, A Navarro, R Asenjo, F Corbera, R Gran, D Suárez, J Núñez-Yañez

Journal of Systems Architecture 98, 27-40. 2019

[DOI] [pdf]

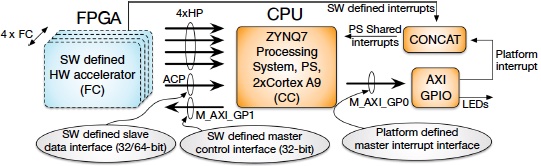

Simultaneous multiprocessing in a software-defined heterogeneous FPGA

JL Núñez-Yáñez, S Amiri, M Hosseinabady, A Rodríguez, R Asenjo, A Navarro, D Suárez, R Gran

Journal of Supercomputing 75 (8), 4096-4097. 2019

[DOI] [pdf]

Exposing abstraction-level interactions with a parallel ray tracer

A Valero, D Suárez Gracia, R Gran Tejero, Luis M. Ramos, A Navarro-Torres, A Muñoz, J Ezpeleta, JL Briz, AC Murillo, E Montijano, J Resano, M Villarroya-Gaudó, J Alastruey-Benedé, E Torres, P Álvarez, P Ibáñez, V Viñals

Proceedings of the Workshop on Computer Architecture Education, 1-8. 2019

[DOI] [pdf]

Cooperative CPU, GPU, and FPGA heterogeneous execution with EngineCL

MA Dávila Guzmán, R Nozal, RG Tejero, M Villarroya-Gaudó, DS Gracia, JL Bosque

The Journal of Supercomputing 75 (3), 1732-1746. 2019

[DOI] [pdf]

Towards the inclusion of FPGAs on commodity heterogeneous systems

MAD Guzman, RG Tejero, MV Gaudo, DS Gracia

2018 International Conference on High Performance Computing & Simulation (HPCS). 2018

[DOI] [pdf]

Mapping streaming applications on commodity multi-CPU and GPU on-chip processors

A Vilches, A Navarro, R Asenjo, F Corbera, R Gran, MJ Garzaran

IEEE Transactions on Parallel and Distributed Systems 27 (4), 1099-1115. 2016

[DOI] [pdf]

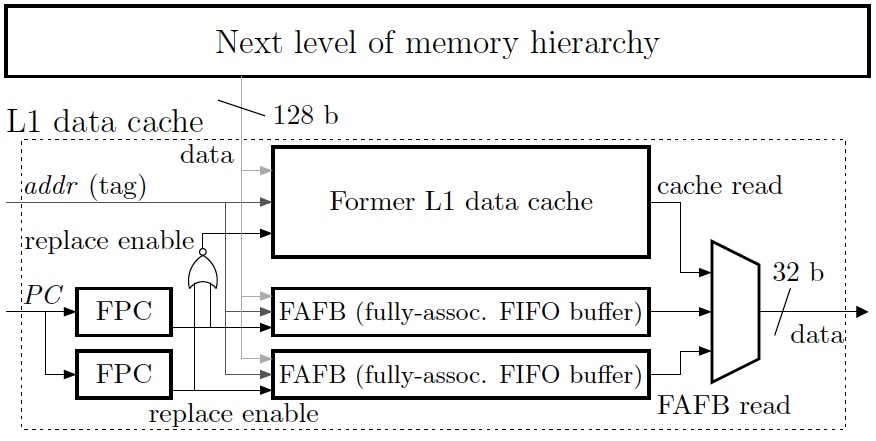

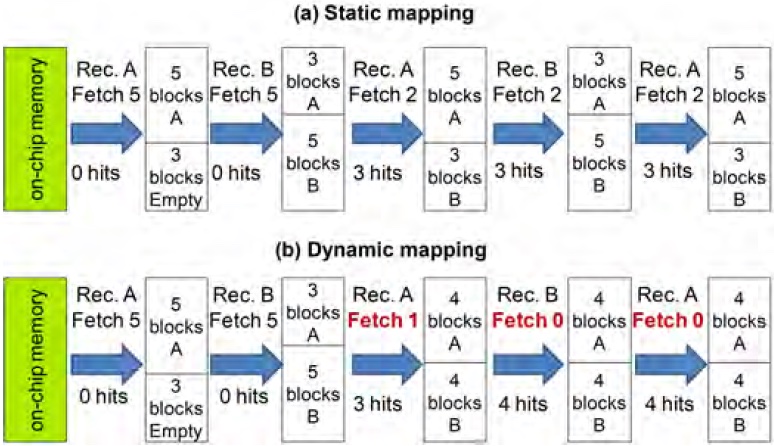

A predictable hardware to exploit temporal reuse in real-time and embedded systems

R Gran, J Segarra, A Pedro-Zapater, LC Aparicio, V Viñals, C Rodríguez

Journal of Systems Architecture 61 (5-6), 227-238. 2015

[DOI] [pdf]

Hardware architectural support for caching partitioned reconfigurations in reconfigurable systems

JA Clemente, R Gran, A Chocano, C del Prado, J Resano

IEEE Transactions on Very Large Scale Integration (VLSI) Systems 24 (2), 530-543. 2015

[DOI] [pdf]

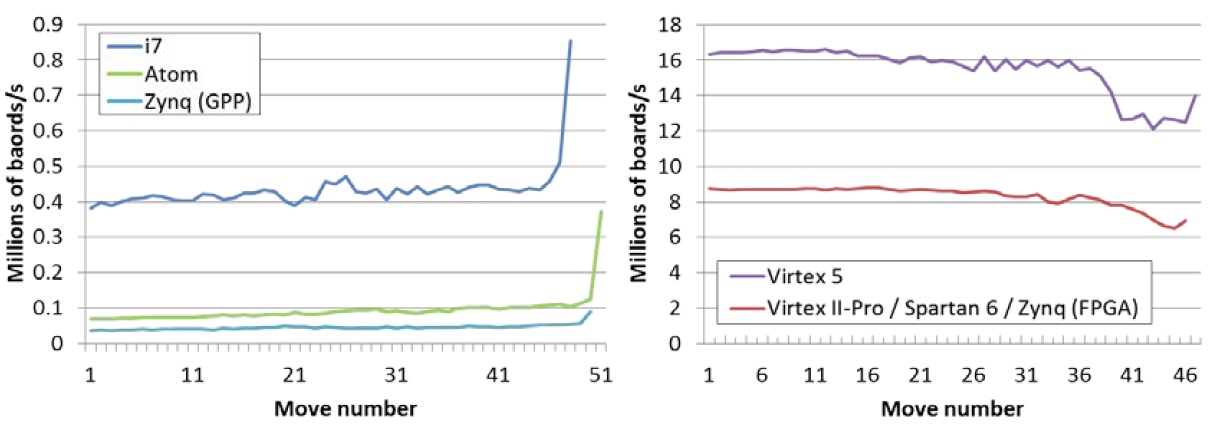

Performance and energy efficiency analysis of a Reversi player for FPGAs and General Purpose Processors

J Olivito, R Gran, J Resano, C González, E Torres

Microprocessors and Microsystems 39 (2), 64-73. 2015

[DOI] [pdf]

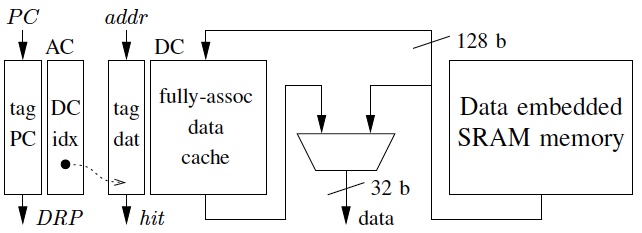

ACDC: small, predictable and high-performance data cache

J Segarra, C Rodriguez, R Gran, LC Aparicio, V Vinals

ACM Transactions on Embedded Computing Systems (TECS) 14 (2), 1-26. 2015

[DOI] [pdf]

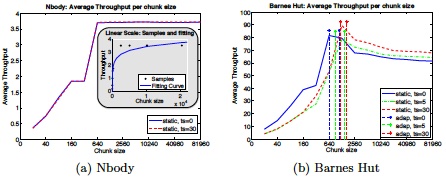

Adaptive partitioning for irregular applications on heterogeneous CPU-GPU chips

A Vilches, R Asenjo, A Navarro, F Corbera, R Gran, M Garzarán

International Conference on Computational Science (ICCS'15). Procedia Computer Science 51, 140-149. 2015

[DOI] [pdf]

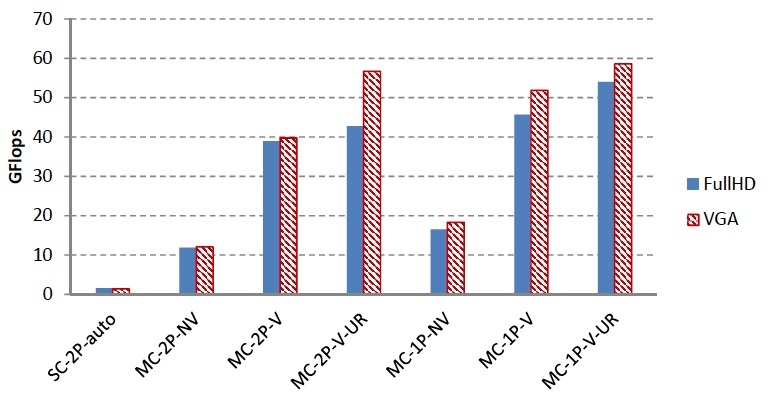

Evaluation of a Feature Tracking Vision Application on a Heterogeneous Chip

R Gran, A Shi, E Totoni, MJ Garzarán

IEEE 26th International Symposium on Computer Architecture and High. 2014

[DOI] [pdf]

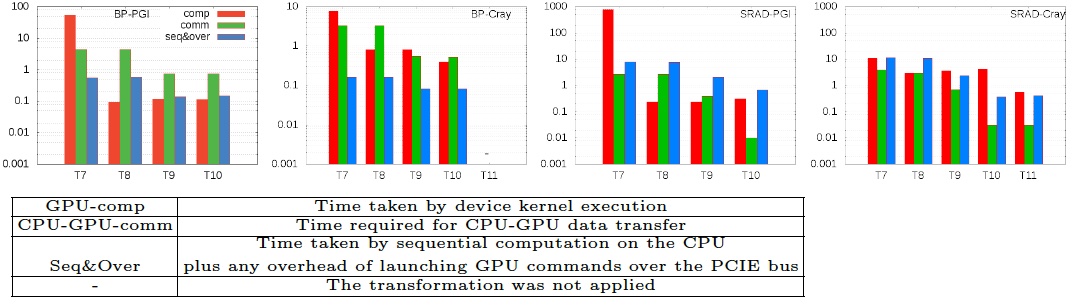

Directive-based compilers for GPUs

S Ghike, R Gran, MJ Garzarán, D Padua

International Workshop on Languages and Compilers for Parallel Computing, 19-35. 2014

[DOI] [pdf]

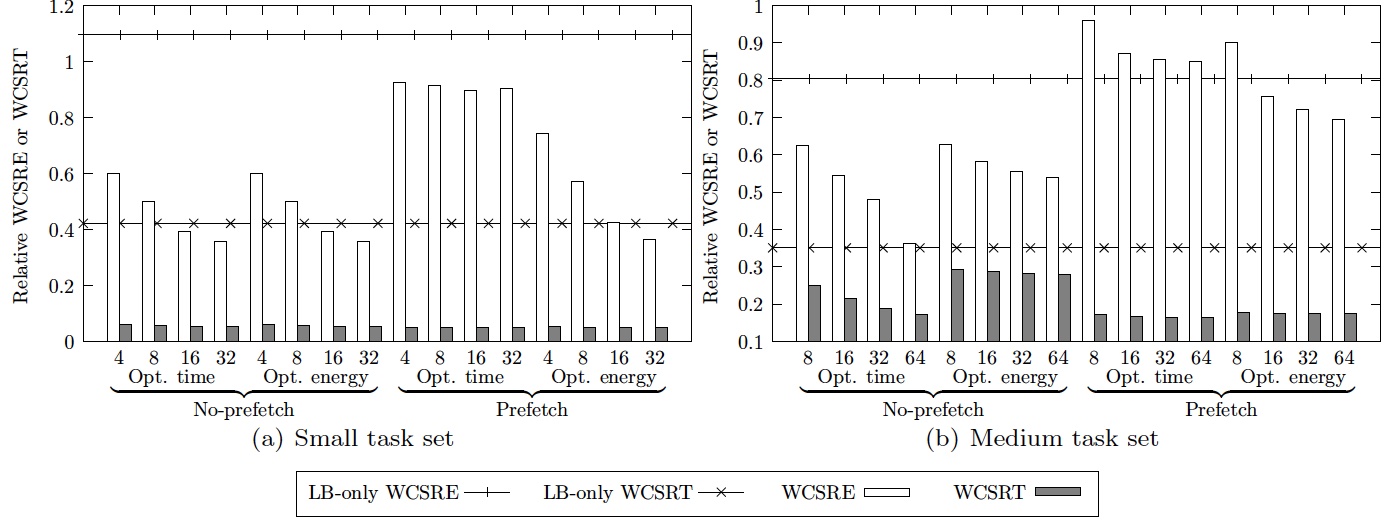

Optimizing a combined WCET-WCEC problem in instruction fetching for real-time systems

R Gran, J Segarra, C Rodríguez, LC Aparicio, V Viñals

Journal of Systems Architecture 59 (9), 667-678. 2013

[DOI] [pdf]

A small and effective data cache for real-time multitasking systems

J Segarra, C Rodriguez, R Gran, LC Aparicio, V Vinals

2012 IEEE 18th Real Time and Embedded Technology and Applications Symposium. 2012

[DOI] [pdf]

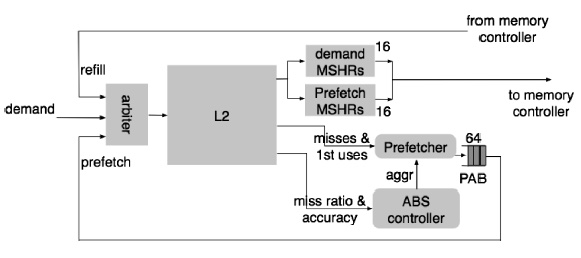

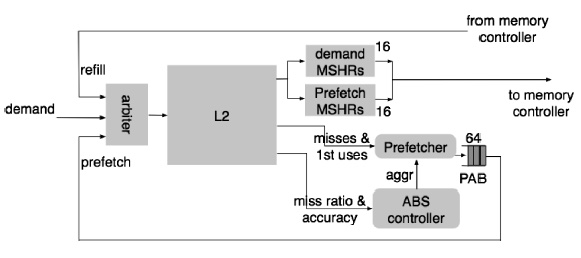

ABS: A low-cost adaptive controller for prefetching in a banked shared last-level cache

J Albericio, R Gran, P Ibánez, V Viñals, JM Llabería

ACM Transactions on Architecture and Code Optimization (TACO) 8 (4), 1-20. 2012

[DOI] [pdf]

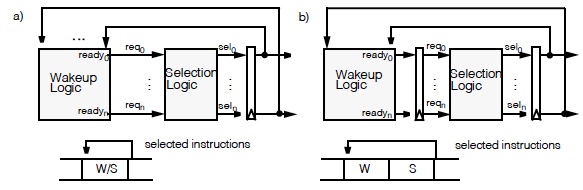

On reducing misspeculations in a pipelined scheduler

R Gran, E Morancho, A Olivé, JM Llaberia

IEEE International Symposium on Parallel & Distributed Processing, 1-12. 2009

[DOI] [pdf]

An Enhancement for a Scheduling Logic Pipelined over two Cycles

R Gran, E Morancho, A Olivé, JM Llaberia

International Conference on Computer Design, 203-209. 2006

[DOI] [pdf]

Despacho 0.18

Edificio Ada Byron

Escuela de Ingeniería y Arquitectura (EINA)

Calle María de Luna nº1, CP 50018, Zaragoza (España)

Correo electrónico:

rgran at unizar dot es