Short Bio

I received the Bachelor Degree in Physics in 1997, a Master Degree in Computer Science in 1999, and the PhD degree in 2005 at the Universidad Complutense of Madrid, Spain. I worked eight years as Assistant and Associate Professor at this University, and collaborated with the Interuniversity Microelectronics Center (IMEC) in Leuven, Belgium. Currently I am Associate Professor at the Computer Eng. Department of the Universidad de Zaragoza (Spain), and a member of the Gaz research group (Computer Architecture group from Universidad of Zaragoza) and the Aragón Institute for Engineering Research (I3A). My research has been focused in hardware/software co-design, task scheduling techniques for multi-processor systems, Digital Logic design using FPGAs, and Dynamically Reconfigurable Hardware.

Teaching Activities

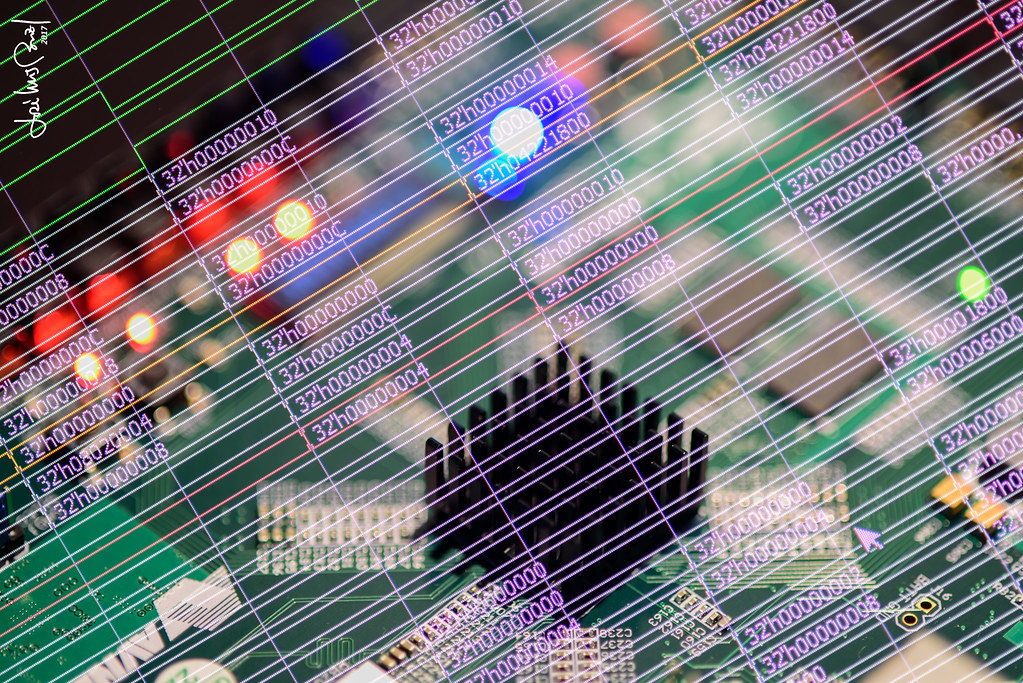

Currently my teaching activities are focused on the Bachelor’s Degree in Informatics Engineering in the School of Engineering and Architecture (EINA) from Universidad de Zaragoza. I teach several subjects in this degree related with computer architecture, embedded systems and FPGA design.

In addition I am very active advising final dissertations and PhD thesis. Three of them have received international awards, and seven of them have received especial mentions as the best (or one of the best) dissertation of the year in different degrees, masters and PhD programs. These dissertations typically focus on FPGA design, embedded systems, and hardware/software codesign.

Research

My research focuses on Reconfigurable Systems, Embedded Systems and Hardware Design. Currently I have three open research lines:

- Development of hardware accelerators: We have developed hardware accelerators for applications from different fields such as Remote Sensing, Image Processing or Artificial Intelligence. We have compared the accelerators with equivalent, and optimized, software versions running both in high performance and in low power processors analyzing not only the performance but also the power and energy consumption. Currentlly I am focused on accelerators for effcient machine learning applications.

- Development of efficient custom SoCs for heterogeneous embedded systems: Our goal is to develop efficient high-performance embedded systems using the new generation of heterogeneous System-on-a-Chip platforms. To this end we profile different applications identifying the computational kernels that can take advantage from hardware acceleration and the different co-design options. After that we design custom hardware blocks and analyze the different hardware/software communication schemes

- On-board processing in remote sensing: We have recently started a new line focusing on deep learning techniques to deal with hyperspectral images. We are looking for high performance energy-efficient solutions that can be executed on board. Currently our work focuses on convolutional neural networks (CNNs) and other machine learning techniques. We want to reduce their computational and memory requirements and design hardware support to execute them more efficiently..

Publications

The most relevant recent publication can be found here

CV

My CV, in spanish, can be found here

Open collaborations

- Universidad Complutense de Madrid. Collaborating with the GHADIR research group (Group of Dynamically Reconfigurable Hardware)

- Department of Technology of Computers and Communications, University of Extremadura. In this case we are collaborating with Professor Antonio Plaza: http://www.umbc.edu/rssipl/people/aplaza/

Awards

Our work has received several international awards:

- First prize in the FPGA design competition organized by the 2009 International Conference on Field-Programmable Technology (FPT). Sydney, Australia

- First prize in the FPGA design competition organized by the 2010 International Conference on Field-Programmable Technology (FPT). Beijing, China

- Second prize in the FPGA design competition organized by the 2012 International Conference on Field-Programmable Technology (FPT). Seoul, Korea

- Forth prize in the FPGA design competition organized by the 2013 International Conference on Field-Programmable Technology (FPT). Kioto, Japan

- First prize in the FPGA design competition organized by the 2014 International Conference on Field-Programmable Technology (FPT). Shanghai, China

- IEEE Real World Engineering Projects Award: awarded for a project that illustrated how FPGAs can be used to solve real-world problems

- 800×600 Best Paper Award of an Engineer under 35 years old in the conference SPIE High-Performance Computing in Remote Sensing.

Contact information

If you want to contact me, just send me an email to: jresano@unizar.es

ente enlace hago una breve presentación de la titulación.