Departamento de Informática e Ingeniería de Sistemas

Memoria de Tesis Doctoral

# FILTERING DIRECTORY LOOKUPS IN CMPS

Autor: Ana Bosque Arbiol Directores: Pablo Ibáñez José M. Llabería Víctor Viñals

Zaragoza

Grupo de Arquitectura de Computadores de la Universidad de Zaragoza

## Abstract

Nowadays, most computer manufacturers offer chip multiprocessors (CMPs) due to the always increasing chip density. These CMPs have a broad range of characteristics, but all of them support the shared memory programming model. As a result, every CMP implements a coherence protocol to keep local caches coherent.

Coherence protocols consume an important fraction of power to determine which coherence action to perform. Specifically, on CMPs with write-through local caches, a shared cache and a directory-based coherence protocol implemented as a duplicate of local caches tags, we have observed that energy is wasted in the directory due to two main reasons.

Firstly, an important fraction of directory lookups are useless, because the target block is not located in any local cache. The power consumed by the directory could be reduce by filtering out useless directory lookups.

Secondly, useful directory lookups (there are local copies of the target block) are performed over target blocks that are shared by a small number of processors. The directory power consumption could be reduced by limiting the directory lookups to only the directory entries that have a copy of the block.

Along this thesis we propose two filtering mechanisms. Each of these mechanisms is focused on one of the problems described above: while our first proposal focuses on reducing number of directory lookups performed, our second proposal aims at reducing the associativity of directory lookups. Several implementations of both filtering approaches have been proposed and evaluated, having all of them a very limited hardware complexity. Our results show that the power consumed by the directory can be reduced as much as 30%.

## Contents

| 1        | Intr | oducti  | on                                                                                                    | 1  |

|----------|------|---------|-------------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Cohere  | ence protocols                                                                                        | 2  |

|          |      | 1.1.1   | Snoop-based coherence protocols                                                                       | 5  |

|          |      | 1.1.2   | Directory-based coherence protocols                                                                   | 6  |

|          |      | 1.1.3   | Other proposals                                                                                       | 8  |

|          | 1.2  | Mecha   | nisms to reduce power consumption in coherence protocols                                              | 9  |

|          | 1.3  | Our pi  | roposal                                                                                               | 11 |

| <b>2</b> | Met  | thodolo | ogy                                                                                                   | 13 |

|          | 2.1  | CMP 1   | model                                                                                                 | 13 |

|          |      | 2.1.1   | Coherence Directory                                                                                   | 14 |

|          | 2.2  | Simula  | ation infrastructure                                                                                  | 18 |

|          |      | 2.2.1   | Simics                                                                                                | 19 |

|          |      | 2.2.2   | CACTI                                                                                                 | 19 |

|          | 2.3  | Bechm   | narks                                                                                                 | 20 |

|          |      | 2.3.1   | SPLASH2                                                                                               | 20 |

|          |      | 2.3.2   | Specweb2005 $\ldots$ | 20 |

| 3        | Red  | lucing  | Directory Lookups                                                                                     | 25 |

|          | 3.1  | 0       | uction                                                                                                | 25 |

|          | 3.2  | Filteri | ng mechanism                                                                                          | 28 |

|          |      | 3.2.1   | ID Filter implementation                                                                              | 29 |

|          |      | 3.2.2   | DPL Filter implementation                                                                             | 33 |

|          | 3.3  | Evalua  | ation                                                                                                 | 36 |

|          |      | 3.3.1   | Coverage                                                                                              | 36 |

|          |      | 3.3.2   | Comparisons avoided in the directory                                                                  | 39 |

|          |      | 3.3.3   | Operations performed by the filter                                                                    | 40 |

|          |      | 3.3.4   | Invalidation messages                                                                                 | 41 |

|          |      | 3.3.5   | Performance                                                                                           | 43 |

|          |      | 3.3.6   | Power reduction                                                                                       | 44 |

|          |      | 3.3.7   | Other cache sizes and new generation technologies                                                     | 45 |

|          | 3.4  | Concli  | 0 0                                                                                                   | 48 |

| 4        | Red | lucing 1 | Directory Lookup Associativity | 51 |

|----------|-----|----------|--------------------------------|----|

|          | 4.1 | Introdu  | uction                         | 52 |

|          | 4.2 |          | ng mechanism                   | 54 |

|          | 4.3 |          | Filter implementation          | 55 |

|          |     | 4.3.1    | Owner Filter states            | 56 |

|          |     | 4.3.2    | Owner Filter update            | 57 |

|          |     | 4.3.3    | Owner Filter entry granularity | 58 |

|          |     | 4.3.4    | Owner Filter operation         | 58 |

|          |     | 4.3.5    | Owner Filter overhead          | 59 |

|          |     | 4.3.6    | Owner Filter evaluation        | 60 |

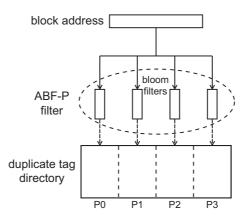

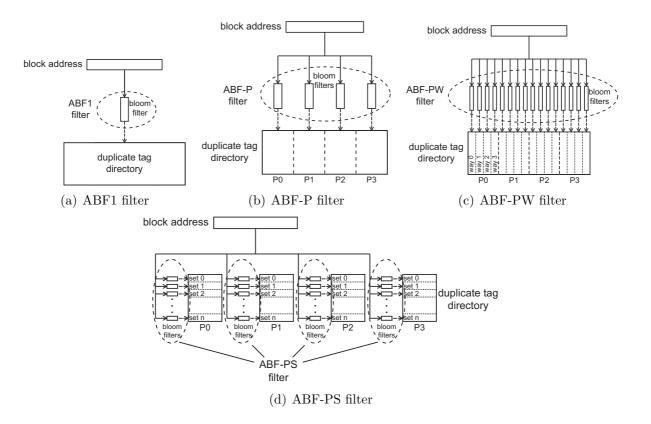

|          | 4.4 | ABF F    | Filter implementation          | 68 |

|          |     | 4.4.1    | ABF Filter Designs             | 69 |

|          |     | 4.4.2    | ABF Filters update             | 72 |

|          |     | 4.4.3    | ABF Filters granularity        | 73 |

|          |     | 4.4.4    | ABF Filters effectiveness      | 75 |

|          |     | 4.4.5    | ABF Filters overhead           | 78 |

|          |     | 4.4.6    | ABF Filters power reduction    | 81 |

|          | 4.5 | Conclu   | -                              | 81 |

|          |     |          |                                |    |

| <b>5</b> | Con | clusior  | lS                             | 83 |

## vi

## Chapter 1

## Introduction

This initial chapter of this thesis summarizes the state of the art of coherence protocols, paying special attention to directory-based protocols and mechanisms that reduce the energy consumed by the coherence protocols. In the last section, we briefly motivate and describe the mechanisms proposed along this thesis as well as the organization of this document in the different chapters.

During the last decades, ever higher operating frequencies have been the main factor driving the performance growth of single-core processors. However, further increases in operating frequencies are increasingly hard to obtain with newer generations of technology. One of the main reasons is the impact of wire delays as feature sizes continue to shrink. To compensate, single-core processors have become increasingly more complex even leading to designs with inefficiencies in power/performance.

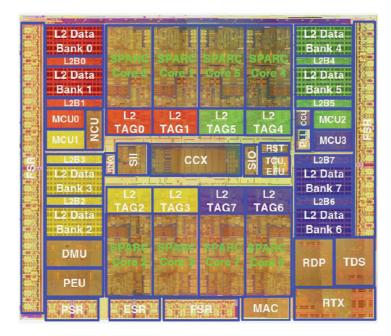

However, the density in the chips continues increasing, which have encouraged the development of chip multiprocessors (CMPs). Nowadays, most computer manufacturers offer CMPs such as the IBM Power7 with 8 cores with four threads each [30], the SUN Rainbow Falls with 16 cores with 8 threads each [47], the Intel Nehalem-EX with 8 cores with 2 threads each [32], the Fujitsu SPARC64 VIIIfx with 8 cores [37], the AMD Phenom II with 6 cores, and the SUN Niagara2 with 8 cores [29]. Figure 1.1 shows Niagara2 chip overview.

All these systems differ from each other in important features like the number of cores, the memory hierarchy, or the interconnection network on-chip. However, in all of them there is at least a local cache level per node and all of them support the shared memory programming model. Thus, every CMP implements a coherence protocol to keep local caches coherent.

Figure 1.1: Niagara2 chip overview. In this chip we can easily distinguish 8 cores (SPARC Core), 8 shared cache banks (L2 TAG and L2 Data Bank), and the interconnection network on-chip (CCX).

## **1.1** Coherence protocols

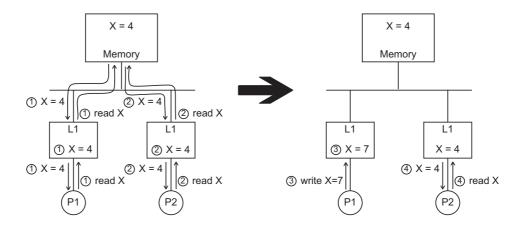

A coherence problem arises in a multiprocessor because every processor access the shared memory through its local cache. Without a coherence mechanism, one processor can write a new value to a memory address and another processor can still access the old value cached in its local cache. Figure 1.2 shows an example of coherence problem. Processors P1 and P2 have local caches and are connected by a bus to main memory. X is a memory address that is read and written by the processors in the order specified by the numbers in the circles. First, P1 reads X. It needs to access main memory and it allocates X in its local cache. P2 also reads X from main memory and keeps X in its local cache. Then, P1 writes a new value in X, but it only updates the value of X in its local cache. Later, when P2 reads X, it reads the value of X from its local copy, so it reads an stale value.

The behavior of a memory system is correct if any read to a memory address returns the most recently written value to that memory address, that is, if the memory system is coherent and consistent. Coherence ensures that all the copies of a memory address in the system are coherent: a) writes to any memory address are propagated to all the processors in the system (write propagation property), and b) writes to a specific memory address are seen in the same order by all the processors (write serialization property).

Consistency defines the memory model of the system, that is, it defines the constraints on the order in which reads and writes to any memory location can appear to execute with respect to one another. Depending on the specific constraints applied, different consistency models can be distinguished. The memory consistency model is defined in the ISA of the architecture and programmers are responsible for writing correct programs under the specific constraints of the consistency model.

**Figure 1.2:** Example of cache coherence problem. Processors P1 and P2 are connected to main memory and both of them have a local cache. They read and write the value of X which is a memory address in the order specified by the numbers in the circles. First, both P1 and P2 read the value of X from memory and they allocate it in their local caches. Then, P1 writes X, but it only updates its local cache. Later, P2 reads X again, but it only access to the copy in its local cache so it gets a stale value.

The most straightforward consistency model is called sequential consistency (SC) [33]. It requires that the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor occur in this sequence in the order specified by its program, like in a sharing-time system. This model is very simple to understand by programmers, but it restricts many of the performance optimizations that modern uniprocessor compilers and microprocessors employ. When using SC most of the memory latency is directly seen by processors as stall time. Thus, other consistency models more relaxed have been defined. For example, Total Store Ordering (TSO) [54] and Processor Consistency (PC) [23] allow reads to be performed before earlier writes in program order; Partial Store Ordering (PSO) [54] allows writes to be performed before earlier writes as long as they access different locations; and Weak Consistency [14], Release Consistency [20], and Relaxed Memory Ordering (RMO) [59] do not guarantee program order besides data and control dependences within a process. In these consistency models, barriers are used to guarantee SC in synchronization points.

The mechanisms to keep a multiprocessor memory system coherent are called cache coherence protocols. These protocols keep track of the sharing of each memory block. Coherence protocols can be classified as directory-based or snoopy-based protocols. Directorybased protocols keep a directory that stores the state of each block of main memory. All transactions should access this structure in order to determine which coherence actions should take place. In the snoopy-based protocols the state of each block of cached data is stored in the local caches, that is, the information about the state of the cached data is distributed. As a result, all memory accesses should be sent to all the local caches in the system.

Coherence protocols can also be classified as invalidation or update protocols. If the write propagation invalidates the local copies of the location written, the protocol is an invalidation protocol. On the other hand, if local copies are updated, it is an update protocol. In any case, next time other processor reads the location written, it gets the last value written either because the local copy has been updated or because the local copy is not valid anymore in its local cache so it is necessary to access either the main memory or the local cache that

keeps the last written value.

The write policy of local caches is very important to define a coherence protocol. If the local caches are write-through, the last value written to any location will always be in main memory. Due to that, the only information that the protocol needs to keep for each block is which local caches keep a copy of the block. On the other hand, if the local caches are write-back, a block written by a store can be only located in the local cache of the processor performing the store. Thus, the coherence protocol keeps not only which local caches keep a copy of a block but the block state in each local cache since it is necessary to know if the block is updated in main memory or not.

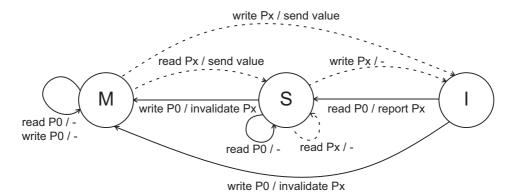

Any coherence protocol is defined by the different states in which a block can be and the transitions among the states. A transition consists of the event that causes the state change and the actions that need to be performed in order to maintain coherence. The events causing state changes are both the requests performed by the processors (reads and writes) and the actions performed to maintain coherence (invalidations or updates depending on the coherence protocol). Figure 1.3 shows an example of a basic coherence protocol based on invalidation with write-back local caches called MSI. The name of this protocol stands for the name of the three states in which a memory block can be: *Modified* (M), *Shared* (S), and *Invalid* (I). A block is *Invalid* for a processor when its local cache does not keep a copy of the block. The state *Shared* identifies a block that is located in the local cache of a processor and that its value has not been modified so the value in main memory is up-to-date and there can be copies in other local caches. A block is classified as *Modified* for a processor when its local cache keeps a copy and it is the only valid copy in the system.

Figure 1.3: State transition diagram for an invalidation coherence protocol called MSI. This protocol has three states: *Modified* (M), *Shared* (S), and *Invalid* (I). The solid lines indicate state changes caused by reads or writes performed by the processor to which this state diagram belongs (read P0 and write P0). The dotted lines indicate state changes due to reads or writes performed by other processors (read Px and write Px). Every line is labeled (A/B) with the event causing the transition (A) and the action performed by the processor (B).

Different coherence protocols have been defined along the last decades. These protocols differ from each other in the write policy of local caches (write-back or write-through), the interconnection network they use, or the responsible for supplying a block (local caches or main memory). Some examples of protocols are: a) write-once [24], Synapse N+1 [19], Berkeley [31], and Illinois (or MESI) [46] which are based on invalidations, and b) Firefly and Dragon [38] which are based on updates.

### **1.1.1** Snoop-based coherence protocols

In snoop-based coherence protocols, the state of each block located in the local caches is maintained by the local caches, that is, the information about the state of any cached block is distributed. To know the state of any block (local caches sharing and state of the copy in main memory), it is necessary to gather in the information about that block in each local cache.

Local caches should be informed of any memory access performed by any processor that it is not a local hit to maintain the information about their local blocks updated. For example, any local cache  $(L1_0)$  has to the informed of a store performed in another local cache  $(L1_1)$  that does not keep a local copy of that block in exclusive state in order to invalidate/update  $L1_0$ 's local copy (if it exists), or any local cache  $(L1_2)$  needs to know when a load miss is performed in other local cache  $(L1_3)$  since it is possible that  $L1_2$  keeps the only copy of that block in the system.

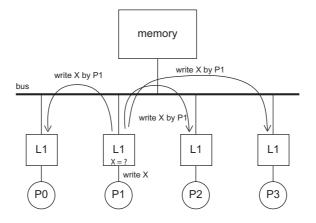

Figure 1.4 shows a multiprocessor with four processors with local caches that are connected by a bus. This multiprocessor keeps coherence by a snoop-based coherence protocol. In this example, P1 performs a write over a memory address X that is not located in its local cache. It is necessary to inform the rest of the local caches about this memory operation, so the write miss is broadcasted on the bus. Depending on the specific protocol and the block state it would be also necessary to send the memory access to main memory.

Figure 1.4: Snoop-based coherence protocol.

Snoop-based protocols became important in multiprocessors that connect the different processors with local caches using a bus since very few changes were necessary to implement the coherence protocol. In the local caches it was only necessary to add a mechanism to snoop the bus and maintain the state of local cached blocks. The reads and writes performed by the processors and sent through the bus keep the caches coherent and the serialization provided by the bus maintains coherency and consistency. However, a bus-based multiprocessor does not scale well.

The process of snooping can be implemented using the local cache tags. However, processor performance might be reduced since processor requests can be delayed by snoop requests. This situation gets worse with multithreading processors as they put more pressure on the local cache. To avoid this performance loss, the local cache tags are duplicated. The

snoop requests access the copy of the local cache tags and only when there is a hit, the state of the corresponding block is accessed to be modified.

Any local cache miss and most writes generate a bus transaction either to request the block or to invalidate or update the local copies of the block. All these transactions perform lookups in all the local caches in the system. However, only a small fraction of these lookups hit in the local caches because the fraction of effective shared cache blocks is small and at any specific point of time these shared blocks are just shared by a few number of processors [41]. Snoop-based protocols consume a significant amount of energy to broadcast requests and perform snoop lookups. This energy is in general wasted because the snoop lookups typically miss in the local caches. In Section 1.2 several mechanism to reduce energy consumption in snoop-based protocols are described.

### 1.1.2 Directory-based coherence protocols

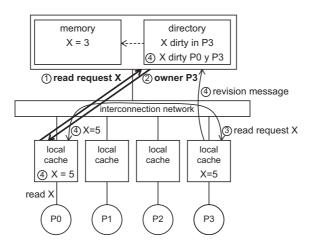

Directory-based coherence protocols maintain the state of every block of main memory in a structure called directory. Any processor request must access the directory and get the state of the target block. Once the state of the block is read, the appropriate actions to maintain coherence must be performed by the directory and the processors involved in the request. Figure 1.5 shows the different actions carried out by a directory-based coherence protocol in a multiprocessor with write-back local caches when a processor performs a read request over a dirty block. Processor P0 reads location X. A dirty copy of X is located in the local cache of processor P3 and this information is kept in the directory. P0 sends a read request to the directory. The directory responses to P0 indicating that P3 keeps the current value of X. Then processor P0 sends a request to P3 and P3 sends the data to P0 and a revision message to the directory in order it updates its state. The final state of X in the directory and the local caches is identified in the figure with the number four inside of a circle.

Figure 1.5: Directory-based coherence protocol in a multiprocessor with write-back local caches.

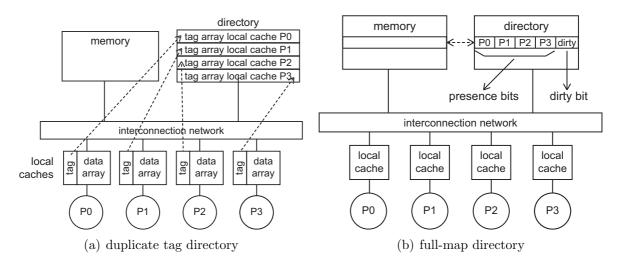

There are two basic schemes to implement a directory: duplicate tags and full-map [56, 9]. Figure 1.6(a) shows a duplicate tag directory scheme. The directory is a separate structure that keeps a copy of all tags and state bits of each line in the local caches [6]. Figure 1.6(b) shows a full-map directory scheme. Each memory block keeps a presence bit

vector and a dirty bit. Each bit of this vector corresponds to one processor or to one local cache. An additional bit is used to identify if the local copies of the block are dirty, that is, the block is up-to-date in memory. The two directory schemes are logically equivalent.

Figure 1.6: Basic directory scheme implementations.

Both directory schemes can be distributed among interleaved memory modules. In a full-map directory, the interleaving for a directory and memory modules is the same. In a duplicate tag directory, the size of the directory depends on the interleaving. If it exists an injective mapping of the cache sets to memory modules then the total directory size is the local cache tag size, e.g., when memory modules are interleaved by the lower address bits of the cache index [55, 57]. In other cases the directory size is bigger than the size of the local cache tags [44].

Several directory schemes have been proposed to reduce the high storage requirements of full-map directories. Some proposals reduce the number of entries in the directory based on the memory hierarchy organization, while other schemes reduce the number of bits per directory entry according to the program behavior.

Sparse directory schemes have less entries than full-map directories [25, 45]. Based on the fact that the number of blocks stored in local caches is much smaller than the number of memory blocks or blocks in a shared inclusive cache, sparse directories are organized as caches. Their entries are dynamically allocated to keep coherence information about the blocks kept in the local caches. The number of blocks that can be cached simultaneously is restricted by cache organization parameters (number of sets and associativity). The management of conflicts increase the miss rate.

Limited pointer directory schemes reduce the number of bits of each directory entry [60, 1, 10]. Since only a few local caches have a copy of a specific block, it is possible to only maintain, instead of a presence bit vector, a fixed number of pointers, each pointing to a processor that currently caches the block. The number of concurrent copies of a block is limited by the number of pointers. When the number of pointers is exhausted and a new processor requests a new copy of the block, overflow strategies are used [4, 10, 42, 1, 25, 34]

Recently, Ferdman et at. design a new directory scheme based on sparse directories, but preventing the set conflicts that diminish performance and reducing the area cost [18]. This directory scheme is intended for many cores since it keeps the power consumption and area utilization nearly constant regardless of core count.

Differences between duplicate tag directory and other directory schemes mentioned above arise in size, lookup method, and retrieved information in a lookup operation. In a duplicate tag directory the lookup is associative, while in a full map directory a lookup is performed using the address to index the structure. The lookup associativity in the duplicate tag directory is the aggregate associativity of the caches it tracks, that is, all possible locations are checked like in a snooping protocol. Both directory schemes identify the processors that have a copy. However, the duplicate tag directory scheme also identifies the way in the set of the local caches. Concerning size, the duplicate tag directory uses the smallest explicit representation of all blocks contained in local caches.

Any coherence request in a snoop-based protocol looks up every local cache. However, most of these lookups are not necessary since the target block is not located in any local cache or it is allocated only in a small number of local caches. These pointless lookups waste energy. Using a full-map directory this problem can be solved since only the local caches that effectively have a local copy of the target block are looked up. Despite accessing only the local caches involved in the coherence request, it requires the local cache tags to be duplicated in order to not delay processor requests causing a performance loss. The problem when using a full-map directory is the directory structure itself. This structure is accessed by any coherence request (dynamic energy consumption) and some schemes have high storage requirements (leakage power). Moreover, any coherence action requires several messages through the interconnection network. Although these messages are point-to-point and they do not have a high energy consumption, they might introduce an important delay in every coherence request.

A duplicate tag directory has smaller storage requirements. However, the directory lookups consume a significant amount of power since they are associative. In fact, all possible locations are checked like in a snooping protocol, though now only the directory structure is accessed. The advantage of a duplicate tag directory is that a directory lookup identifies not only the local caches that have a copy of the target block, but the way in the local caches in which the block is located. Thus, invalidation messages only consist of the index and the way of the local cache that has to be invalidated. Moreover, as invalidation messages does not need to access the local cache tag array, the processor requests are never delayed. So it is not necessary to duplicate the local cache tag array.

#### 1.1.3 Other proposals

Recently, Zebchuk et. al. [61] propose a directory structure that use an implicit and conservative representation of the blocks located in the local caches instead of the explicit representation used in conventional directory schemes. The structure organization is like a duplicate tag directory but the blocks located in each set of the local caches are represented using a bloom filter. In this proposal, the storage overhead of the directory structure is smaller than in conventional directories organizations, but it requires to introduce several extensions to a base coherence protocol.

This proposal is in between snoop-based and directory-based protocols. Unlike directorybased protocols, the tagless directory is not able to limit local cache lookups performed by coherence requests to the ones performed over blocks present in the local caches. However, not all the local caches are looked up for every coherence request as it is necessary in a snoop-based protocol. The tagless directory requires a small structure that scales nicely with the number of cores and that does not have a high energy consumption. However, to maintain the directory up-to-date, it is necessary to add new coherence messages or at least to add more information to the coherence messages performed by a directory-based protocol.

## **1.2** Mechanisms to reduce power consumption in coherence protocols

During the last decade several techniques to filter out coherence actions have been published. The proposed mechanisms try to reduce either local cache lookups performed by coherence requests or directly the broadcast messages. In order to reduce the coherence actions a filter structure is necessary. This structure is either placed together with the local caches or distributed in the on-chip network.

First, we will go over proposals that use a filter which is placed together with the local caches. The filters are small structures that are accessed before any snoop-induced local cache tag lookup is performed and try to avoid useless local cache lookups. They determine whether the target block might be located or definitely it is not present in the local cache. The former case requires a local cache lookup while, in the latter case, the cache lookup is known to "miss", that is, it is useless and it can be avoided.

Jetty [41] proposes for a SMP system three different filters: a) a filter that keeps blocks not present in the local cache (got from last snoop-induced tag lookups that missed), b) a filter that keeps a superset of the blocks in the local cache (updated with any allocation or replacement), and c) a mix of the two first filters. Ekman et al. [15] analyze the power performance of Jetty in a CMP system. They conclude that, as the local cache sizes are smaller than in a SMP system, the filter and the local caches energy consumption are similar. Thus, Jetty is not an interesting mechanism for CMP systems.

Salapura et al. [48, 49] proposes a mechanism similar to Jetty, but their main interest is to filter useless snoop-induced lookups not to reduce power consumption but to improve performance. Snoop-induced lookups can delay processor requests causing a performance loss, so if the number of snoop-induced lookups is reduced, less processor requests will be delayed and processor performance will improve. The filter used is a Stream Register which keeps a superset of the blocks in the local cache. A Stream Register consists of a set of base addresses with a corresponding bit mask. The bit mask identifies which base address bits are significant. An address is consider to be present in a Stream Register if it matches all base address significant bits from any entry.

When the goal of the filter is to avoid broadcasts, the filters are accessed before any

coherence request is sent by any processor. Depending on the specific mechanism, the filters determine either whether the target block is shared by any other processor or not, or the subset of processors that shared the target block. If the target block is not shared at all, broadcast is not necessary. If the subset of processors sharing the target block is identified, the broadcast can be replaced with as many point-to-point messages as necessary.

PST (Page Sharing Table) [16] is a unit integrated with the TLB that keeps track for each page of how many blocks the local cache has and which processors have blocks from that page. Using this structure coherence requests are snooped only by those local caches that have blocks located in the same page as the target block.

RegionScout [40] identifies which regions are not shared. A region is defined as a continuous, aligned memory area. RegionScout uses two structures: NSRT (Not Shared Region Table) and CRH (Cached Region Hash). The first one keeps track of all regions that are identified as not shared by any other processor. A not shared region is identified after a coherence request over a block included in that region. Processors indicate for any coherence requests that reach them if any block of the same region of the target block is located in its caches or not. If every processor classifies the region of a block as not shared, then that region is included in the NSRT. The CRH is a Bloom filter that keeps a superset of all regions locally cached. It is used to identify not shared regions by a processor without accessing its local cache. An access to a memory address that belongs to any region in the NSRT does not require a broadcast since that memory address is not shared by any other processor.

Cantin et al. [8] propose a filter that, like RegionScout, keeps sharing region information for each processor. This proposal requires a structure called RCA (Region Coherence Array). This structure keeps the state of any region of which there is at least a locally cached block. As the information kept for any region is precise and it indicates not only the presence of a block belonging to that region but the state of it, the proposed structure is bigger than in RegionScout. However, they are able to remove more coherence requests.

Strauss et al. [53] analyze how to implement adaptive forwarding algorithms in network rings using filters that indicate the probability of a snoop-induced lookup to hit in the local cache. These filters are similar to the ones in the previous proposals [41, 40, 8].

All previous proposals use both processors requests (reads and writes) and coherence requests performed by other processors to keep the filter structures up-to-date. There are also some proposals that use filters that classify blocks as shared or not shared based on program semantics. Dash et al.[12] proposes to add information regarding shared memory regions during software development and compilation. If a processor request access a block that belongs to a region identified as non-shared, none coherence request will be necessary. Ballapuram [5] proposes a similar idea. It describes two different techniques. The first one, called SSP (Selective Snoop Probe), labels blocks as stack and non-stack. Stack blocks are never shared so no coherence actions are performed for them. For the non-stack blocks, a superset of the locally cache blocks is kept using a bloom filter to filter snoop-induced local cache tag lookups. The second technique, called ESP (Essential Snoop Probe) labels at compilation time variables (stack, global, and heap) as blocks that do not need coherence actions since they are not shared. There are also proposals that distribute the filter over the on-chip network for snoopybased and directory-based protocols. Agarwal et. al. [2] propose adding a region tracker structure in each output port of the routers. This structure indicates which regions are not located in the local caches of the processors reached from a specific port, so useless broadcast messages are not sent. Jerger [28], in a coarse-grain like directory-based protocol, adds counting bloom filters to each output port of the routers in order to not broadcast useless invalidation messages addressed to the local caches reached from a specific port.

## 1.3 Our proposal

We propose filtering mechanisms to reduce the power consumed by a duplicate tag directory in a CMP which has multithreaded processors with local instruction and write-through data caches, and an inclusive shared cache. (A detailed description of the CMP is in Section 2.1.)

As processors are multithreaded, local caches are highly accessed by the processors. A directory organization such as a full-map directory requires a lookup in the local cache tags for every invalidation. As a result, if processor requests and invalidations sent from the directory share the same local cache port, thread execution can be delayed. Thus, the local cache tags require two ports so that thread performance is not diminished. An alternative is to replicate the cache tags [52, 11]. This replica is located side-to-side with the local cache tags and it is used by invalidations to set the state bits of the cached blocks.

The replica of the local cache tags can be located in the other side of the interconnection network and be used as a duplicate tag directory. The full-map directory is removed. Now, when an invalidation is sent, the local cache set and way to invalidate is already identified in the message, and a local cache lookup is not needed. As the replica of the local cache tags is located together with the inclusive shared cache, it is possible to keep pointers to the shared cache tags (set index and way) instead of the local cache tags themselves. Consequently, the duplicate tag structure is much smaller [29].

Every directory lookup requires an expensive associative lookup in the duplicate tag structure. However, we analyze the behavior of several programs and we conclude that: a) an important fraction of directory lookups are useless since there are no local copies of the target block, and b) the directory lookups that are useful are performed over blocks that are shared by a small number of processors. Based on these observations, we propose two filtering mechanisms. The first filtering mechanism tries to identify in advance directory lookups that are useless and filters them out. This filter reduces significantly the number of directory lookups performed (Chapter 3). The second filtering mechanism tries to identify which processors have local copies of the target block of a directory lookup, that is, the sharers of the target block. Once the sharers are determined, the directory lookup only checks the directory entries corresponding to those processors, and therefore, the directory lookup associativity is reduced (Chapter 4).

The rest of this dissertation is organized in four chapters. Chapter 2 describes the methodology used in the evaluation of the proposed filtering mechanisms: CMP model chosen, simulation infrastructure developed, and benchmarks used. Chapter 3 describes the first filtering mechanism which reduces the number of directory lookups performed.

Chapter 4 introduces the second filtering mechanism proposed which reduces the directory lookup associativity. Finally, we conclude this thesis in Chapter 5 with a summary of the contributions and publications derived from this research.

## Chapter 2

## Methodology

Along this chapter we describe the evaluation methodology. First, we introduce the CMP model that we assume in all the experiments carried out to evaluate the different mechanisms proposed in this thesis. Next, we describe the most important characteristics of the simulation infrastructure. Finally, we present the benchmarks used and we introduce their main characteristics.

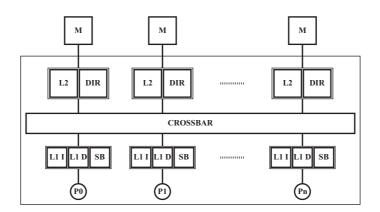

## 2.1 CMP model

Figure 2.1 shows the CMP configuration we assume along this thesis. It is a CMP with 8 in-order multithreaded cores and a memory hierarchy similar to the one in Niagara 2. The first cache level is local to each core, and is composed of an instruction cache (L1 I) and a write-through no-write-allocate data cache (L1 D). Each core has also a store buffer (SB) with several entries per thread that contain all outstanding stores. The second-level cache (L2) is shared among all the cores and is inclusive, that is, all data in the local caches must also be in the shared cache. It is divided into different banks interleaved by second-level cache block size. Two crossbars communicate the two cache levels.

A write-invalidate directory-based protocol is used to maintain cache coherence among the local caches. The directory is distributed among the second-level cache banks, keeping close to each bank the information about the blocks mapped to it. Table 2.1 presents the specific parameters we chose for the memory hierarchy. All of them are based on Niagara 2 memory hierarchy parameters.

CMPs that use write-through local caches (as the one modeled in this paper) require more bandwidth than CMPs that use write-back local caches (like Piranha [6]), because all stores must access the shared cache. However, the extra bandwidth guarantees that data is always updated in the shared cache. Thus, the latency to access shared data does

**Figure 2.1:** CMP model with a first-level local cache per core (instruction cache, data cache and store buffer) and a second-level shared cache divided in several banks.

| L1 D size            | 8KB      | L2 size            | 4MB        |

|----------------------|----------|--------------------|------------|

| L1 D associativity   | 4-way    | L2 number of banks | 8          |

| L1 D block size      | 16B      | L2 associativity   | 16-way     |

| L1 I size            | 16KB     | L2 block size      | 64B        |

| L1 I associativity   | 8-way    | L2 latency         | 7 cycles   |

| L1 I block size      | 32B      | L2 MSHR            | 8          |

| Crossbar arbitration | 3 cycles | Store              | 8 entries  |

| Crossbar latency     | 3 cycles | Buffer             | per thread |

| Physical address     | 40 bits  | Memory latency     | 117 cycles |

Table 2.1:

Memory hierarchy parameters

not depend on how many caches are sharing it, but it is only increased by contention in the interconnection network. Moreover, in a system with write-back local caches, local caches are responsible for serving dirty blocks when they are requested by other processors. These requests can delay the access of a processor to its local caches, reducing processor's performance. In a system with write-through local caches, local caches do not serve any other processor requests.<sup>1</sup>

Like in Niagara 2 [55], instruction/data block exclusivity is maintained in the local caches, that is, the same block can not be at once in both instruction and data caches (across all cores). The directory is responsible for ensuring instruction/data exclusivity. The shared cache block size is larger than the block size of the local caches. Thus, copies of different subblocks from the same shared cache block can reside in local caches of different types (instruction/data).

### 2.1.1 Coherence Directory

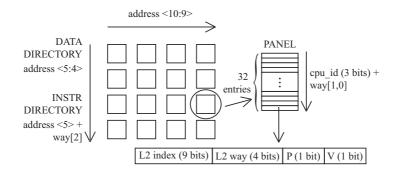

We assume a directory similar to that of Niagara 2 [55], which consists of a duplicate of the local cache tags. The directory is split into instruction and data directories, replicating the organization of the local caches. The directory in each bank is implemented as a CAM

<sup>&</sup>lt;sup>1</sup>The bandwidth requirements to implement local write-through caches is so high in many-core systems (which is not the target of this thesis), that makes it unaffordable. However, in this scenario, a practical implementation would be to organize the many-core system in small clusters and perform cache coherency at the cluster level. Each of these clusters would be the CMP modeled in this thesis.

structure whose area requirements is O(PxNL1/NBL2), being P the number of processors, NL1 the number of lines in the local caches and NBL2 the number of banks of the shared cache. The size of this structure also depends on the local cache tag size. As the shared cache is inclusive, any local cache block is allocated in the shared cache. Thus, the local cache block tag in the directory could be replaced by the set index and way of the corresponding shared cache block. Since in the modeled CMP the shared cache tag array is accessed before the directory, set index and way are available on time to access the directory. This information requires fewer bits, and so, the directory size and its power consumption are smaller.

A lookup in a duplicate tag directory is associative, so it is expensive in terms of energy consumption. However, this lookup identifies not only the processors that have a copy, but also the way in the set of the local caches. Block invalidations are performed by sending to all involved processors a message that includes the local cache set index and the way(s) in the set to invalidate. So, there is no need of local cache lookups to identify which block to invalidate. The directory is also responsible for identifying which stores have to update a block in the local cache of the processor performing the store. Thus, stores update local caches when the acknowledgement message is received. This message, like invalidation messages, includes the way that has to be updated.

#### **Directory Organization**

Duplicate instruction and data directories have a similar structure, but they are accessed in a different way depending on the kind of memory access to the shared cache that performs the access to the directory.

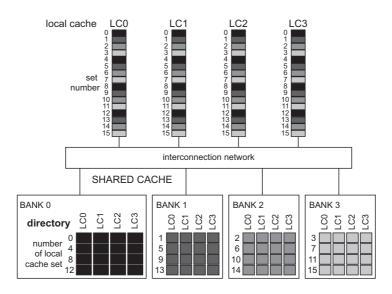

In order to understand better the directory organization, let us first assume that the shared cache block size is the same as the local cache block size. The shared cache is split in several banks and it is interleaved by its block size. The directory is also split in order that each shared cache bank only keeps the fragment of the directory corresponding to the blocks mapped to that bank. Blocks located in contiguous local cache sets are mapped to different shared cache banks and therefore to different directories. Thus, the number of local cache blocks assigned to a particular directory is (NLCS/SCB)\*LC, being NSLC the number of local cache sets, SCB the number of shared cache banks, and LC the number of local caches. Figure 2.2 shows an example of how the blocks located in the first set of a local cache are mapped to the directory of the first shared cache bank, blocks located in the second set are mapped to the directory of the second shared cache bank, and so on. Blocks located in a specific set are mapped to a single directory, independently of the local cache where they are located.

However, as the local cache block size is smaller than the shared cache block size in our CMP model, several contiguous local cache sets are mapped to the same shared cache bank. This number is equal to the ratio between the shared cache and the local cache block size. As before, the number of blocks mapped to a particular directory is (NLCS/SCB)\*LC. Figure 2.3 shows the same system as Figure 2.2, but now the local cache block size is half the shared cache block size. The number of sets in the local cache is doubled and the mapping to the shared cache banks changes. Blocks located in two consecutive local cache sets are mapped

Figure 2.2: Mapping of local cache blocks to shared cache banks and directories when the shared cache and the local caches have the same block size.

to the same shared cache bank: the first two local sets are mapped to the first shared cache bank, the second two local sets are mapped to the second shared cache bank, and so on.

Our CMP model has 8 shared cache banks interleaved by 64B blocks, and 8 local data caches, each one with 128 sets of associativity 4, and block size of 16B (see Table 2.1). Blocks located in four contiguous local cache sets are mapped to the same directory since the banks are interleaved by 64B blocks and the local cache block size is 16B. The total number of blocks mapped in a specific directory is 512 (4-way  $\times$  16 sets  $\times$  8 local caches).

Each directory puts together blocks located in the same set of all the local caches because it is the minimum amount of blocks that need to be looked up in any directory lookup. This number of blocks is 32 (4 blocks/set  $\times$  8 local caches). Moreover, the directory is also organized in order to make easy to access blocks located in contiguous sets in the local caches. The reason is that depending on the shared cache access, the corresponding directory lookup can require to look up all these blocks. Figure 2.4 shows how the directory is organized in 16 different panels (using SUN's terminology [55]) of 32 entries which correspond to the blocks located in the same set of all the local data caches. Each panel entry keeps only the block located in a particular local cache and in a specific way of the local cache set that the panel corresponds to. Any directory lookup determines the panel(s) which has to be looked up using some address bits of the target block. Then, all the entries of the panel(s) are compared to the target block. The local caches that keep a local copy and the way where the copy is located are determined by the entries with a positive result from the comparison.

In a similar way, the instruction directory of a shared cache bank tracks 512 blocks (8-way  $\times$  8 sets  $\times$  8 local caches). It is also organized in panels of the same size as the data directory. Differences are due to larger cache block size and higher associativity in the local instruction caches.

Figure 2.3: Mapping of local cache blocks to shared cache banks and directories when the shared cache block size is twice the local cache block size.

Figure 2.4: Data or instruction directory structure of Niagara 2 and how they are accessed.

#### **Directory Operation**

Any access to and any eviction from the shared cache performs a lookup in the directory. Along this thesis, we call "memory operations" to all these accesses and evictions from the shared cache, namely, loads and instruction fetches that miss in the local caches, stores and evictions from the shared cache. If the shared cache and the local cache had the same block size, the directory lookup for all memory operations would require the same number of comparisons, involving all the elements of a specific local cache set in every local cache. However, in our CMP model local and shared cache block sizes are different. Thus, some lookups require twice or four times more comparisons.

Below we describe the memory operations and the actions performed in the directory for each one:

• Load-miss: It is a load that miss in the local data cache. The directory entry that corresponds to the local cache location in which the block will be allocated is updated with the missing address tag. In order to assure instruction/data exclusivity, it is

| memory operation      | data directory | instruction directory |  |

|-----------------------|----------------|-----------------------|--|

| load-miss             | update         | lookup (64)           |  |

| ifetch-miss           | lookup (64)    | update                |  |

| store                 | lookup (32)    | lookup (64)           |  |

| shared cache eviction | lookup (128)   | lookup $(128)$        |  |

**Table 2.2:** Actions performed in the data and instruction directories for every memory operation in the shared cache. For each lookup, the number of comparisons performed is enclosed. The shaded cells identify the actions that are unnecessary in a system without data/instruction exclusivity.

necessary to invalidate all the copies of the 16B block (local data cache block size) in all the local instruction caches. The address of this 16B block determines a specific set in the local instruction caches. 64 comparisons are performed since there are 8 local instruction 8-way associative caches.

- *Ifetch-miss*: It is an instruction fetch miss in the local instruction cache. The behavior is the same as in a load-miss but, instead of the data directory, the instruction directory is updated and all the copies of the 32B block (local instruction cache block size) are invalidated in the local data caches. Thus, the blocks allocated in two local data cache sets are looked up. 64 comparisons are performed since there are 8 local data 4-way associative caches.

- *Store*: As the local data cache is write-through, every store accesses the shared cache. The copy of the local tags in both directories, data and instruction, are looked up in order to send invalidations to all the local caches that have the block. The address of this block determines one local data cache set and one local instruction cache set. Thus, 32 and 64 comparisons are performed in the data and the instruction directories respectively.

- *Eviction*: It is an eviction from the shared cache. As inclusion is enforced in the system, the shared cache victim block must be removed from the local caches. Instruction and data directories are looked up in order to send invalidations to all the local caches that have a copy of the 64B evicted block (shared cache block size). Thus, up to two 32B blocks in the local instruction caches and four 16B blocks in the local data caches are invalidated. So, 128 comparisons are performed in each directory.

Table 2.2 summarizes the actions performed for every memory operation and the number of comparisons performed by the lookup actions. The shaded cells identify the actions that are unnecessary in a system without data/instruction exclusivity.

Update actions are mandatory in order to keep always an exact copy of the tags of the local caches in the directory.

## 2.2 Simulation infrastructure

This section presents the simulator used to model the CMP described in the previous section and the cache power model chosen to estimate the dynamic energy and the leakage power of the directory and the proposed filters.

## 2.2.1 Simics

We use a Simics-based simulator. Simics is a platform for full-system multiprocessor simulation [36]. This thesis focuses on CMPs which are intended for multiprocessor workloads such as databases or web servers. These applications highly depend on the operating system memory management and scheduling, so they cannot be simulated independently from the operating system. As a result, we chose Simics as simulation platform since it is capable of running unmodified commercial OSs and applications.

Simics simulates processors at the instruction-set level, including the full supervisor state. It supports a wide variety of processors such as UltraSparc, Alpha, x86, PowerPC, MIPS, or ARM. We configured Simics to model a SPARC V9 target system running Solaris 9. We simulated a system with 8 in-order, blocking, 1.2GHz processors with 4 threads each that share a 8 GB memory. Due to simulation time restrictions, the non-numerical applications are executed in a system with 8 non-multithreaded processors.

Simics is only a functional simulator by default, but it can be extended with detailed processor and memory system timing models. We decide to use in-order, blocking processors that perform one instruction per cycle. As all our contributions are intended to improve the power consumption of the coherence directory, which is part of the memory hierarchy, we require to model the timing of each memory system access.

We connect a timing model to the memory space of Simics accessed by all the instruction fetches and data accesses. We completely developed this timing model using the Simics API. This timing model accurately models the memory hierarchy of our CMP model. We model the different components of the hierarchy, their timing, and the contention in the different shared components such as the interconnection network, the shared cache banks, or the local caches shared by several threads. The main characteristics of this memory hierarchy are detailed in Section 2.1 and its parameters are described in Table 2.1. The consistency memory model of this memory hierarchy is Total Store Order (TSO).

## 2.2.2 CACTI

We use CACTI 6.5 [43] to estimate the dynamic energy and the leakage power for the shared cache, the coherence directory and the proposed filters. CACTI is an integrated cache and memory access time, cycle time, area, leakage, and dynamic power model. We modified CACTI to model CAM structures because the coherence directory is implemented as a CAM structure. These modifications were based in the CAM structures implemented in McPAT. McPAT (Multicore Power, Area, and Timing) is an integrated power, area, and timing modeling framework for multithreaded, multicore, and manycore architectures [35].

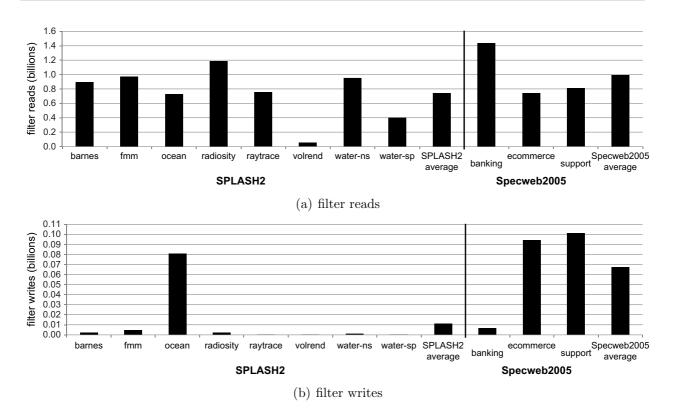

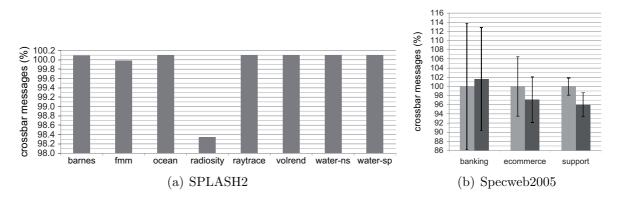

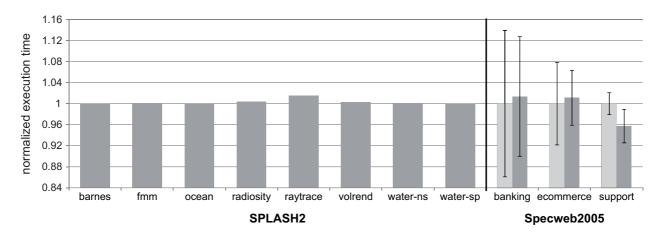

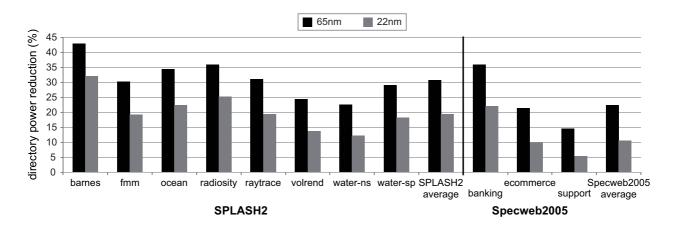

The shared cache, the coherence directory and the proposed filters were modeled using a 65nm technology with a target frequency of 1.2 GHz. The average dynamic power consumption is computed based on activity statistics of the shared cache, the filters, and the data and instruction directories along the execution of the benchmarks.

## 2.3 Bechmarks

We use SPLASH2 and Specweb2005 to evaluate the different filtering mechanisms proposed in this thesis. Both SPLASH2 and Specweb2005 are benchmark suites that consists of several workloads. Along this thesis, we show the different metrics for all the workloads and also the average for all the workloads in each benchmark suite, that is, we compute the average for SPLASH2 and for Specweb2005. Depending on the metric, the average is the arithmetic or the geometric mean.

This section introduces the main characteristics of SPLASH2 and Specweb2005 and how we configure them. We also present a characterization analysis of the Apache web server using Specweb2005 as URL request generator.

### 2.3.1 SPLASH2

We use the applications of the SPLASH2 benchmark suite [50]. In order to adapt the SPLASH2 workloads to our simulated scenario, we scaled the input dataset up as proposed by Monchiero et al. [39]. For water-nsquared and water-spatial we were only able to scale the datasets to 2k and 4k particles, respectively to bound the simulation time. We execute the whole parallel section of each benchmark. Table 2.3 shows the applications used, the corresponding datasets, the billions of cycles and executed instructions, the local data and instruction cache miss rate (L1 data miss rate and L1 instr miss rate) per instruction, and the shared cache miss rate (L2 miss rate) per instruction.

| benchmark      | dataset           | instr    | cycles   | L1 data   | L1 instr  | L2 miss |

|----------------|-------------------|----------|----------|-----------|-----------|---------|

| Dencimark      | uataset           | $(10^9)$ | $(10^9)$ | miss rate | miss rate | rate    |

| barnes         | 64K particles     | 4.97     | 0.62     | 2.48      | 0.004     | 0.045   |

| fmm            | 64K particles     | 9.57     | 1.20     | 1.51      | 0.016     | 0.052   |

| ocean          | 1026x1026         | 5.99     | 0.91     | 6.21      | 0.008     | 1.746   |

|                | -largeroom,       |          |          |           |           |         |

| radiosity      | -ae 5000          | 7.45     | 0.94     | 3.13      | 0.177     | 0.003   |

|                | -en 0.050 -bf 0.1 |          |          |           |           |         |

| raytrace       | balls4            | 5.77     | 0.79     | 9.44      | 0.008     | 0.001   |

| volrend        | head              | 0.63     | 0.08     | 1.67      | 0.030     | 0.010   |

| water-nsquared | 2192 particles    | 13.79    | 1.72     | 0.80      | 0.001     | 0.004   |

| water-spatial  | 4096 particles    | 4.02     | 0.50     | 1.32      | 0.001     | 0.002   |

Table 2.3: SPLASH2 benchmarks, the corresponding datasets, billions of cycles and instructions executed, local data and instruction miss rate per instruction, and shared cache miss rate per instruction.

### 2.3.2 Specweb2005

Specweb2005 [27] is a URL request generator. We use Specweb2005 to analyze and evaluate our proposals for the Apache web server. In this subsection we first describe Specweb2005 and the Apache web server configuration. Then, we explain how we run our simulations to analyze only the behavior of the Apache web server. Finally, we show a characterization of the Apache web server using Specweb2005.

#### Specweb2005 description

Specweb2005 is a software benchmark product developed by SPEC. It is designed to measure a system's ability to act as a web server servicing static and dynamic page requests. It is composed for three different workloads: **banking**, **ecommerce**, and **support**, in an attempt to cover the different scenarios in which a web server is commonly used.

- **Banking** simulates a bank web site in which the clients, once logged in, are able to do operations like getting the list of all the transactions done in the last month, checking the state of a payment or transferring money. All requests in this workload are SSL based (Secure Sockets Layer).

- Ecommerce is designed to simulate a Web server that sells computer systems. Each client could pass by three different phases: browse, customization and purchase. Only the last phase is SSL based.

- **Support** is to test the ability to download large files. It simulates a vendor's *support* web site. In this workload SSL is never used. The user will browse the catalog or search in it until he/she finds the file of interest and then downloads it.

In Specweb2005 the sequence of operations made by a client is defined by a Markov chain. Every operation is done in a different web page, that is, the web page in which the login is done is different from the one in which the clients check the last transactions in their bank accounts. The Markov chain states are the different web pages or operations, and the transactions among them are the different options that the clients could take.

Another important parameter is the thinking time which is the time between two consecutive requests made by the same client, that is, the time that the client needs to read the web page that has just received before requesting the next one. In all the workloads of Specweb2005 we set the thinking time to zero in order to be able to see a bigger number of transactions in the few seconds of the benchmark that we are simulating.

Specweb2005 has four major logical components: the clients that send HTTP requests to the server and receives the responses, the prime client that initializes and controls the execution, and collects statistics, the web server that handles the requests of the clients, and the back-end simulator (BeSim) that emulates a back-end application server.

#### Apache web server configuration

We use Apache 2.0.63 [26] configured with the process model *worker*, which implements a hybrid multi-process multi-threaded server in which a single control process (the parent) is responsible for launching child processes. Each child process creates a fixed number of server threads as well as a listener thread which listens for connections and passes them to a server thread for processing when they arrive. In our configuration the number of child processes is fixed along the whole simulation to 4 with 150 server threads each. We also configured Apache for using *posix threads* for all the synchronization tasks.

#### Simulation environment

Simics is capable of running unmodified applications, so we only need to set up the same environment of Specweb2005 as in a real machine. We require a machine for the Apache web server, another one for the clients, and one more for the BeSim. Simics allows us to simulate these machines and connect them by a simulated network. Table 2.4 describes the different machines that we are simulating and also the software applications that are necessary in each machine. We are only interested in the behavior of the Apache web server. Thus, we only take statistics from the machine running the Apache web server.

|            | Description                      | Hardware     | Software                         |

|------------|----------------------------------|--------------|----------------------------------|

| Clients    | The clients run in this machine  | 4 processors | JRE HotSpot 1.5.0                |

| Besim      | Back-end simulator that emulates | 4 processors | Apache $2.0.55 + $ library       |

|            | a back-end application server    |              | FastCGI 2.4.0                    |

| Web server | System Under Test in which the   | 8 processors | Apache $2.0.55 + $ libraries php |

|            | Apache web server is running     |              | 5.1.2 & OpenSSL 0.9.8a           |

Table 2.4: Simulated machines and software applications necessary for Specweb2005

Table 2.5 indicates how many simultaneous sessions are running for each workload. Web servers present high time and space variability [3] and, on top of that, we cannot simulate Specweb2005 workloads until their completion due to simulation time restrictions. To minimize web server variability, we run several simulations for each workload performing the same number of web transactions. All these simulations are run after fast forwarding the period of ramp up of Specweb2005 [51]. To determine the number of web transactions in each workload, we warm the caches for 0.75 billion cycles and then we measure the number of web transactions for 2.25 billion cycles. Table 2.5 shows the number of web transactions performed, the average billions of instructions executed for each workload, and the number of simulation runs. We use the mean of the simulations in all the graphics in this thesis in which Specweb2005 appears.

| workload  | simultaneous | web    | instr    | simulation |

|-----------|--------------|--------|----------|------------|

| workioad  | sessions     | trans. | $(10^9)$ | runs       |

| banking   | 200          | 100    | 15.52    | 30         |

| ecommerce | 1000         | 1200   | 8.07     | 15         |

| support   | 1400         | 2200   | 8.07     | 10         |

**Table 2.5:** Specweb2005 workloads, the corresponding simultaneous sessions, the number of web transactions, billions of instructions executed and number of simulation runs.

### Apache web server characterization with Specweb2005

A commercial workload like the Apache web server has a behavior different from more traditional scientific applications. We decide to analyze the memory behavior of Apache using Specweb2005 as URL request generator. We measure the shared cache miss rate per data access, the breakdown of execution time, and the number of web pages requested.

As we do not require a detailed memory hierarchy, we decide to perform this characterization using Simics and VASA [58]. VASA is a configurable high-performance multiprocessor simulation package for Simics that can model all the components of the memory hierarchy, but it does not model contention. The memory hierarchy is slightly different to the memory hierarchy used in the rest of the thesis. Table 2.6 presents the most important parameters of this memory hierarchy. All workloads were executed with 200 simultaneous clients and only one simulation run per workload of 10 billion cycles was performed.

| Processor speed             | 1.2 GHz       |

|-----------------------------|---------------|

| store buffer size           | 4 entries     |

| store buffer line size      | 32 bytes      |

| store buffer read latency   | 1 cycle       |

| L1 instruction cache        | perfect       |

| L1 data cache size          | 32 KB         |

| L1 data cache associativity | 4-way         |

| L1 data cache line size     | 32 bytes      |

| L1 data cache latency       | 1 cycle       |

| L1 data cache write policy  | write-through |

| L2 data cache size          | 1 MB          |

| L2 data cache associativity | 4-way         |

| L2 data cache line size     | 32 bytes      |

| L2 data cache latency       | 12 cycles     |

| L2 data cache write policy  | write-back    |

| memory access latency       | 150 cycles    |

| network bandwidth           | 8 bytes/cycle |

| network latency             | 12 cycles     |

Table 2.6: System on-chip parameters

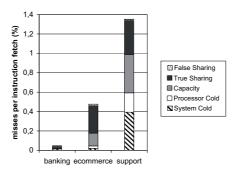

Figure 2.5 shows the shared cache miss rate per instruction fetch and classifies the misses into three basic categories based on the classification presented by Dubois et al. [13]: cold, capacity (replacement), and sharing. A miss is classified as a cold miss if the block has never been in this processor's cache before. A miss is a sharing miss if the last time the block was in the cache it was invalidated due to a store performed by another processor. All other misses are capacity misses.

Figure 2.5: Shared cache data miss rate for the three workloads of Specweb2005.

The classification between capacity and sharing depends on the size of the cache. As we are interested in knowing the true communication in the application independent of the cache size, we change a little the classification assuming an infinite cache for coherence. In this classification a miss is a sharing miss if the block has been modified since the last time it was in the processor's cache. All other misses are capacity misses.

We decided to split the cold misses in two different categories: system cold misses and processor cold misses. In the first ones, the block has never been written by any processor.

We also split the sharing misses in two categories: true sharing and false sharing misses. A sharing miss is classified as true sharing if the bytes accessed by the processor during the lifetime of the block in the cache have been modified by another processor since the last time the block was in the cache. It is classified as false sharing miss in any other case.

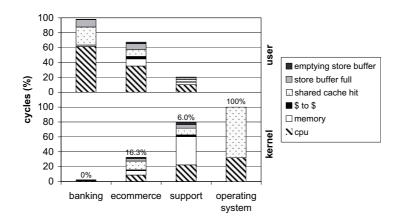

Figure 2.6 shows the breakdown of execution time into six components: cpu time, shared cache hit access, memory access, cache to cache service, store buffer full stall cycles, and emptying the store buffer due to the execution of atomic instructions. The upper part of the graph shows the breakdown for the cycles executed in user level and the bottom part presents the same data, but for privilege level. The number on top of the privilege level cycles is the percentage of idle time. We get this number from the statistics of the *mpstat* command. We use this command along the whole simulation since it report statistics about the usage of the cpus: user, system, waiting, and idle time.

Figure 2.6: Breakdown of cycles for the three workloads of Specweb2005.

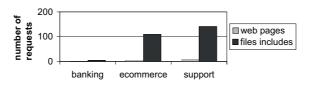

Figure 2.7 shows the number of web pages requested by the clients and the number of extra files included inside them. When a file is sent from the server to the client we always call that a transaction without taking into account if it is the main page or just a file included in it.

Figure 2.7: Number of web pages and files included requested per 100 billion cycles for the three workloads of Specweb2005.

## Chapter 3

## **Reducing Directory Lookups**

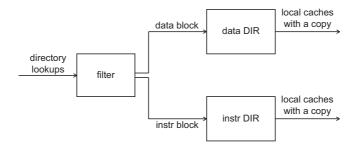

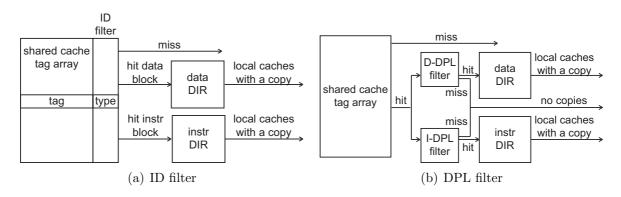

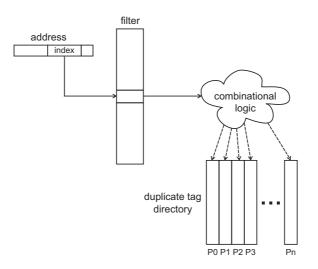

This chapter describes a filter which reduces the number of directory lookups performed. This filter takes into account that, in general, the sets of memory addresses of instructions and data are disjoint and it classifies blocks as data or instruction blocks.

We propose two different filter implementations: the Instruction-Data filter (ID filter) and the Decoupled filter (DPL filter). The ID filter keeps explicit filtering information for every block in the shared cache identifying it as a data or an instruction block. The DPL filter keeps a superset of the blocks that belong to each stream (data or instruction). We require a D-DPL filter for the data directory and a I-DPL filter for the instruction directory. The information kept in these filters is decoupled from the shared cache organization.

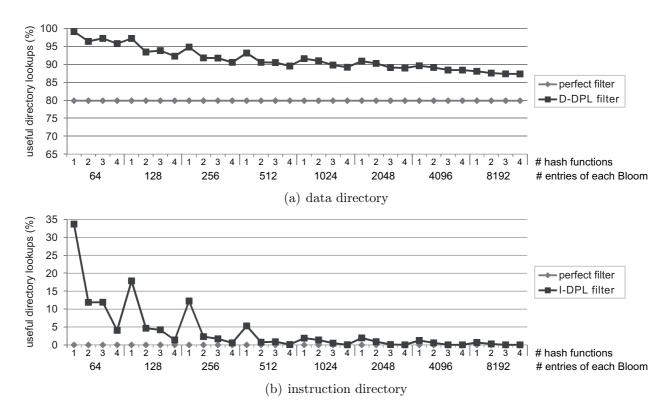

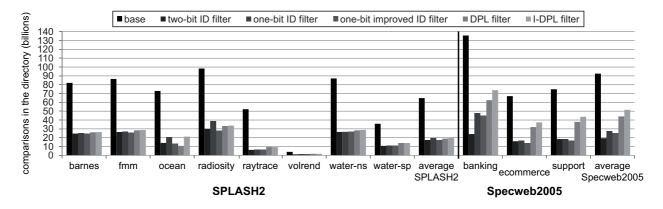

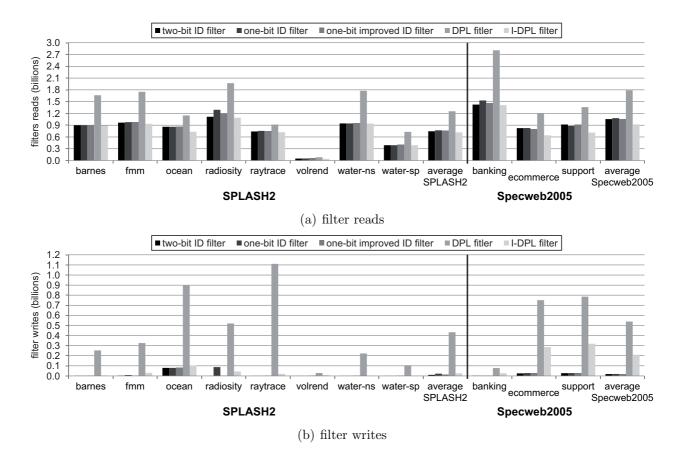

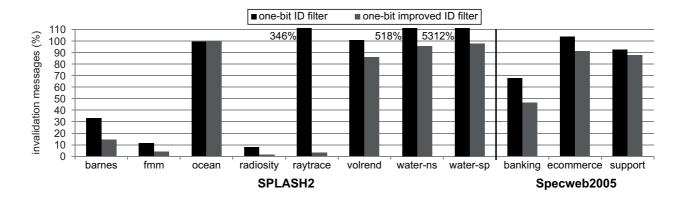

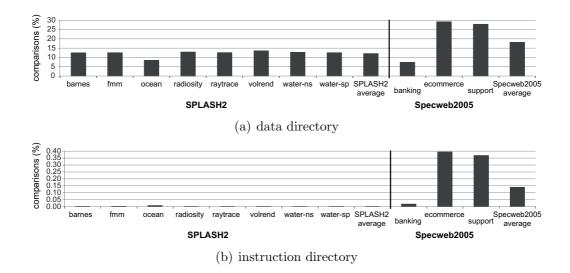

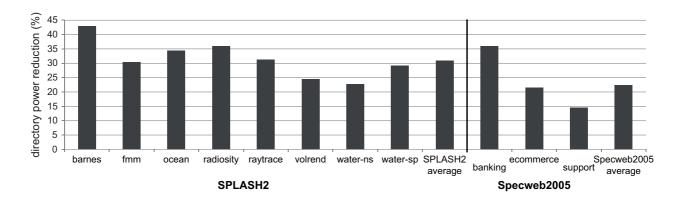

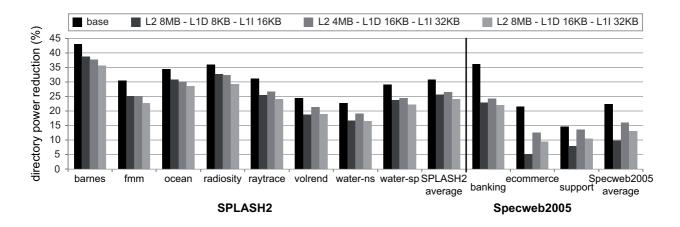

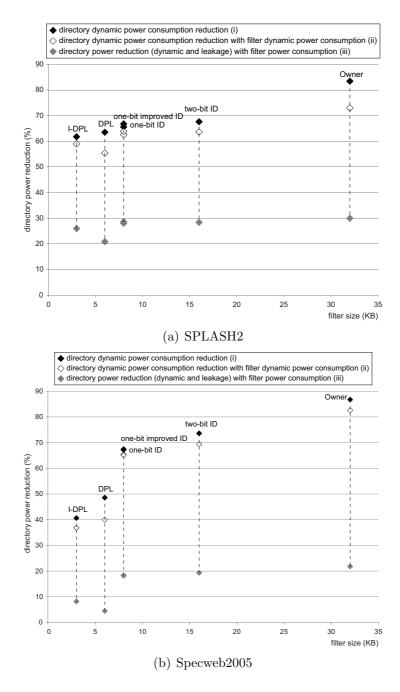

Our results show that, for SPLASH2, the proposed filters reduce the number of directory lookups performed by 60% while directory power consumption is reduced by 28%. For Specweb2005, the number of directory lookups performed is reduced by 68% (44%), while directory power consumption is reduced by 19% (9%) using the ID filters (the I-DPL filter).

This chapter is organized as follows. Section 3.1 motivates why the proposed filtering mechanism can work. Section 3.2 describes the filtering mechanism and details the proposed implementations. Section 3.3 evaluates the most important characteristics of the proposed filters. Finally, Section 3.4 concludes this chapter.

## 3.1 Introduction

The sets of memory addresses of instructions and data (values of program counters of the executed instructions and addresses of referenced data) are disjoint. The computer memory is organized into segments: code segment, stack segment, and heap segment which are mapped to different memory regions. The code of a program is allocated in the code segment, while

the static and dynamic variables used in the functions of this program are allocated in the stack segment and the heap segment, respectively. Thus, data and instructions addresses are expected to be different. However, though it is the common situation, it is not always true. There are special cases in which data and instructions are allocated to the same region so a cache block belongs to the data and the instruction stream simultaneously. Two examples of this situation are self-modifying code and constants located in the code segment:

- *Self-modifying code* Self-modifying code is code that alters its own instructions while it is executing. This code performs stores over blocks that later will be accessed to fetch the instructions to execute, that is, first it accesses a block as data and then as an instruction.

- Constants located in the code segment Sometimes compilers locate program constants along with the instructions that use them. Thus, a cached block could contain instructions and constants (data).

If any of the previous situations takes place, a block can be located simultaneously in both the data and the instruction local caches. As a result, a directory lookup always requires to look up both the data and the instruction directory.

The CMP model we are using along this thesis has a local instruction and data cache, and an inclusive shared cache. In this CMP, coherence is maintained by a coherence directory implemented as a duplicate of the local cache tags. Therefore, we can distinguish a data and a instruction directory (see Section 2.1).

Stores and evictions from the shared cache should invalidate all the copies of the target block in the local caches. In order to do that, the data and the instruction directory should be looked up since the system cannot assure that the target block has only been accessed as instruction or as data.

Instruction fetches (loads) that miss in the local caches should invalidate all the copies of the target block in the local data (instruction) caches to maintain instruction/data exclusivity (see Section 2.1). To carry out the corresponding invalidations, the data (instruction) directory should be looked up.

Table 3.1 gathers together the actions performed in the directory by any memory operation: loads and instruction fetches that miss in the local caches, stores, and evictions from the shared cache.

| memory operation                  | data<br>directory | instruction<br>directory |

|-----------------------------------|-------------------|--------------------------|

| load-miss                         | update            | lookup                   |

| ifetch-miss                       | lookup            | update                   |

| store                             | lookup            | lookup                   |

| eviction from the<br>shared cache | lookup            | lookup                   |

**Table 3.1:** Actions performed in the data and instruction directories for any shared cache access or eviction from the shared cache.

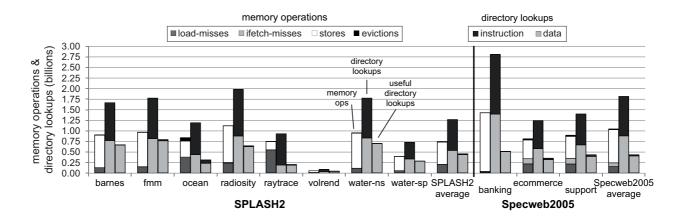

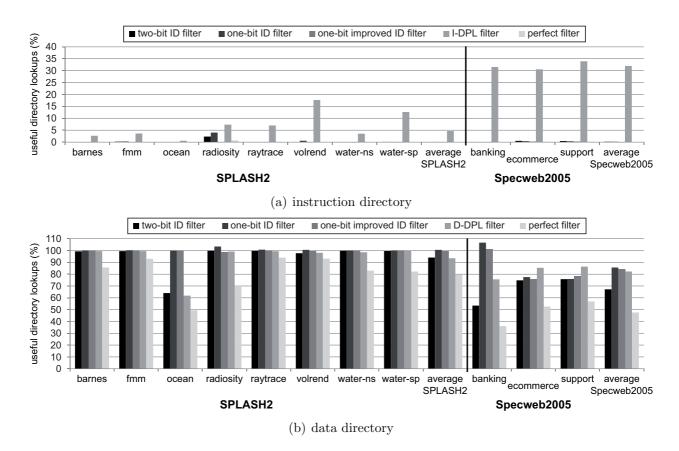

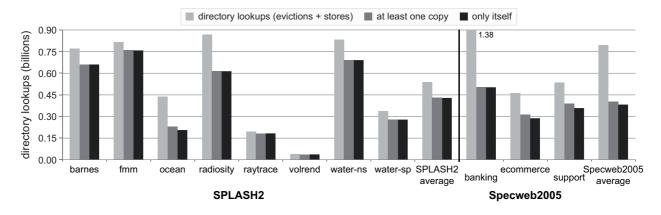

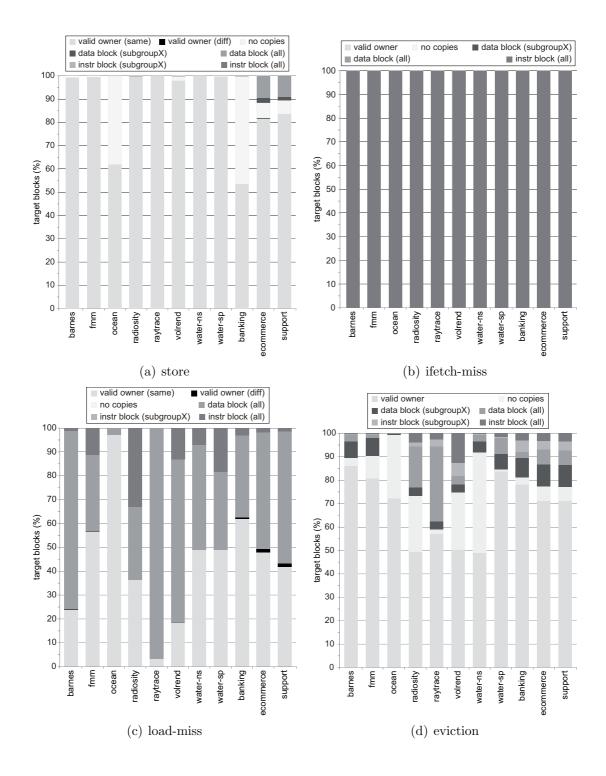

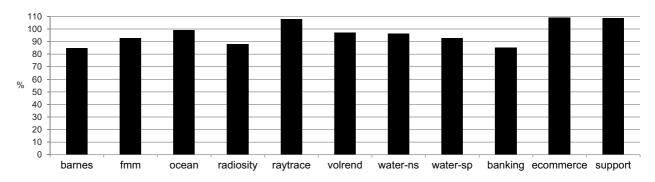

Figure 3.1: The first column for each benchmark represents the billions of memory operations that access the shared cache categorized as load-misses, ifetch-misses, stores and evictions. The second column collects the billions of directory lookups in each directory. The third column represents the billions of "useful" directory lookups in each directory

Any block cached in the shared cache has been usually accessed either as data or as instructions since, as we explain before, in general, the sets of memory addresses of instructions and data are disjoint. As a result, the local copies of a block cached in the shared cache are located either in the local data caches or in the local instruction caches. Therefore, a directory lookup performed in both the data and the instruction directory can only "hit" in one of them, that is, only one of the directories looked up reports that there are copies of the target block in the local caches that it represents. For example, an eviction from the shared cache performs a directory lookup in the data and the instruction directory. In general, if the directory lookup hits in the data directory, it misses in the instruction directory, and the other way around. In the same way, most of the times, instruction fetches (loads) that only require to lookup in the data (instruction) directory do not find a copy of the target block in that directory since a block accessed by an instruction fetch (load) generally has been previously accessed only by instruction fetches (loads or stores), and so, there are copies of that block only in the local instruction (data) caches.

We call "useless lookups" to the directory lookups that miss in a directory since there are no copies of the target block in any local cache represented by that directory. We call "useful lookups" lo the directory lookups that hit, that is, at least one local cache represented by the directory keeps a copy of the target block.

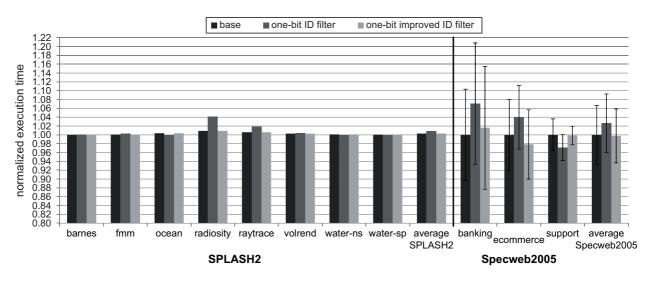

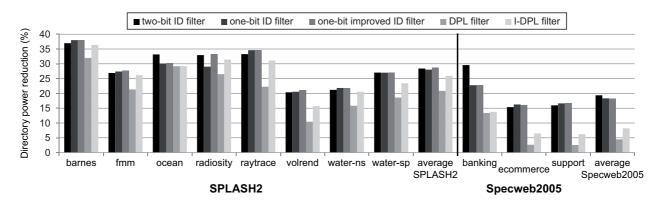

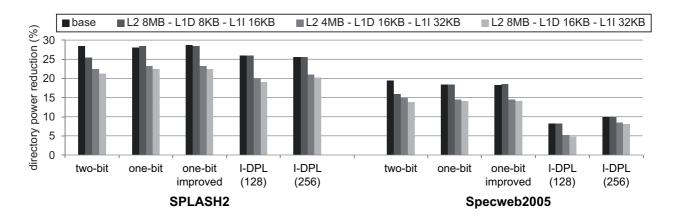

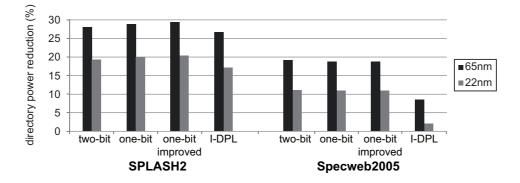

If we identify useless lookups in advance, we could prevent them to be performed. If their number is significantly important, the energy consumed by the directory could be reduced. Now, we analyze the number of useless lookups in the different benchmarks we use (see Section 2.3).