# UNIVERSIDAD DE ZARAGOZA Tesis Doctoral

Prebúsqueda Hardware, Soporte para Reducción, y Almacenamiento de Estado Especulativo en Multiprocesadores de Memoria Compartida.

Autor: María Jesús Garzarán Arnau Directores: Dr. D. Víctor Viñals Yúfera

Dr. D. José María Llabería Griñó Dr. D. Josep Torrellas Jovaní

gaZ

CENTRO POLITECNICO SUPERIOR

DEPARTAMENTO DE INFORMATICA E INGENIERIA DE SISTEMAS GRUPO DE ARQUITECTURA DE COMPUTADORES DE ZARAGOZA

## Prebúsqueda Hardware, Soporte para Reducción, y Almacenamiento de Estado Especulativo en Multiprocesadores de Memoria Compartida

Memoria presentada para optar al grado de Doctora Ingeniera en Informática por

#### Doña María Jesús Garzarán Arnau

Departamento de Informática e Ingeniería de Sistemas Universidad de Zaragoza Marzo de 2002

Dirigida por

Dr. D. Víctor Viñals Yúfera Dr. D. José María Llabería Griñó Dr. D. Josep Torrellas Jovaní

Departamento de Informática e Ingeniería de Sistemas

Universidad de Zaragoza

A mis padres Santiago y Angeles, y a mis hermanos.

#### Acknowledgements

First of all, I would like to thank my thesis advisors for their guidance and support. Víctor Viñals introduced me to the interesting world of multiprocessors and encouraged me to work in this area. Jose María Llabería has always been very supportive. He has always been ready to work with me, and to talk with me on the phone whenever I needed to discuss something. I also want to thank Josep Torrellas for hosting me during my stay at Urbana-Champaign, and for suggesting that I work on speculation. Special thanks to all of them, not only for their advising, but also for their attention and friendship.

I am also very grateful to all the members of the I-ACOMA group at Urbana-Champaign and my colleagues at the architecture group in Zaragoza. I especially thank Milos Prvulovic, my work-mate during my stay at Illinois; I had many insightful discussions with him. Special thanks also to José Martínez for all his encouragement. He has always been one of my strongest supports at Illinois. José Luis Briz and Pablo Ibáñez have also been very supportive during all these years. They helped me with the initial work on hardware prefetch and with reading this thesis.

Thanks also to my friends Pablo, Juan, Silvia, and María Angeles. They have been truly good friends, who have always listened to me and offered their help. I also owe special gratitude to Luis, for all the support he has given me.

Finally, I want to thank my parents, my brothers and their wives, and the rest of my family. I dedicate the work of all these long years to my parents and brothers. I could not have done it without their love and support.

This work has been supported in part by the Ministry of Education of Spain under contracts TIC 1998-0511-C02-02 and TIC 2001-0995-C02-02; National Science Foundation under grants CCR-9734471M ACI-9872126, EIA-9975018, CCR-9970488M, EIA-0081307, and EIA-0072102; and by gifts from IBM, Intel, and Hewlett-Packard.

## Contents

| 1 | Intr | oduction                                                          | 1  |

|---|------|-------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                        | 1  |

|   |      | 1.1.1 Hardware Prefetch                                           | 4  |

|   |      | 1.1.2 Parallelizing Reductions                                    | 5  |

|   |      | 1.1.3 State Buffering in Speculative Thread-Level Parallelization | 6  |

|   | 1.2  | Thesis Contributions                                              | 8  |

|   | 1.3  | Thesis Organization                                               | 9  |

| 2 | Pat  | tern Characterization                                             | 17 |

|   | 2.1  | Introduction                                                      | 17 |

|   | 2.2  | Measured Patterns and Environmental Setup                         | 19 |

|   |      | 2.2.1 Measured Patterns                                           | 19 |

|   |      | 2.2.2 Workload and Methodology                                    | 23 |

|   | 2.3  | Pattern Distribution                                              | 23 |

|   | 2.4  | Sequence Length                                                   | 27 |

|   | 2.5  | Summary                                                           | 29 |

| 3 | Har  | dware Prefetch in Bus-based Multiprocessors                       | 33 |

|   | 3.1  | Introduction                                                      | 33 |

|   | 3.2  | Related Work                                                      | 34 |

|   | 3.3  | Environmental Setup                                               | 37 |

|   |      | 3.3.1 System with prefetch                                        | 38 |

|   |      | 3.3.2 Workload and Methodology                                    | 40 |

|   | 3.4 | Perform | mance Model                                             | 40         |

|---|-----|---------|---------------------------------------------------------|------------|

|   | 3.5 | Evalua  | ation                                                   | 42         |

|   |     | 3.5.1   | Base System                                             | 42         |

|   |     | 3.5.2   | Discussion of Prefetching Alternatives                  | 42         |

|   | 3.6 | Summ    | ary                                                     | 48         |

| 4 | Sup | port f  | or Parallel Reductions in Scalable Shared-Memory Multi- |            |

|   | pro | cessors |                                                         | <b>5</b> 3 |

|   | 4.1 | Introd  | $\operatorname{uction}$                                 | 53         |

|   | 4.2 | Paralle | elization of Reductions in Software                     | 55         |

|   |     | 4.2.1   | Background Concepts                                     | 55         |

|   |     | 4.2.2   | Parallelizing Reductions                                | 56         |

|   |     | 4.2.3   | Drawbacks in Scalable Multiprocessors                   | 58         |

|   | 4.3 | Private | e Cache-Line Reduction (PCLR)                           | 58         |

|   |     | 4.3.1   | Overview of PCLR                                        | 59         |

|   |     | 4.3.2   | Implementation of PCLR                                  | 60         |

|   |     | 4.3.3   | Summary                                                 | 66         |

|   | 4.4 | Evalua  | ation Methodology                                       | 67         |

|   |     | 4.4.1   | Simulation Environment                                  | 67         |

|   |     | 4.4.2   | Applications                                            | 68         |

|   | 4.5 | Evalua  | ${f tion}$                                              | 69         |

|   |     | 4.5.1   | Impact of PCLR                                          | 69         |

|   |     | 4.5.2   | Scalability of PCLR                                     | 72         |

|   |     | 4.5.3   | Impact of FP-Unit Speed                                 | 72         |

|   | 4.6 | Additi  | onal Use of PCLR                                        | 73         |

|   |     | 4.6.1   | Dynamic Last Value Assignment in Software               | 73         |

|   |     | 4.6.2   | Using PCLR for Last Value Assignment                    | 74         |

|   |     | 4.6.3   | Advanced Support                                        | 75         |

|   | 4.7 | Relate  | d Work                                                  | 77         |

|   | 4.8 | Summ    | ary                                                     | 77         |

|   |     |         |                                                         |            |

| 5 | Tra   | deoffs | in State Buffering for Speculative Thread-Level Parallelization | 83  |

|---|-------|--------|-----------------------------------------------------------------|-----|

|   | 5.1   | Introd | uction                                                          | 83  |

|   | 5.2   | Buffer | ing State Under Speculative Parallelization                     | 85  |

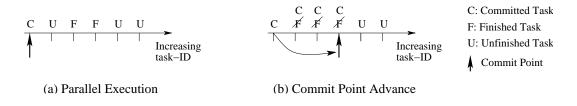

|   |       | 5.2.1  | Basics of Speculative Parallelization                           | 85  |

|   |       | 5.2.2  | Challenges in Buffering State                                   | 88  |

|   |       | 5.2.3  | Application Behaviour                                           | 90  |

|   |       | 5.2.4  | Analogy to Register File Management                             | 92  |

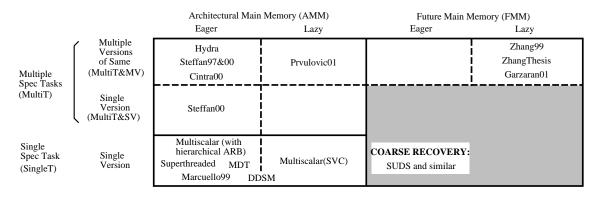

|   | 5.3   | Taxon  | omy of Approaches                                               | 93  |

|   |       | 5.3.1  | Speculative State Composition                                   | 93  |

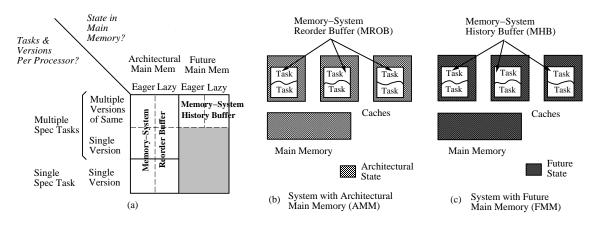

|   |       | 5.3.2  | Novel Taxonomy of Approaches                                    | 94  |

|   |       | 5.3.3  | Mapping Proposed Schemes to the Taxonomy                        | 95  |

|   | 5.4   | Imple  | mentation Issues                                                | 99  |

|   |       | 5.4.1  | Implementing a Distributed MROB                                 | 99  |

|   |       | 5.4.2  | Implementing a Distributed MHB                                  | 100 |

|   |       | 5.4.3  | Operations To Support in a Distributed MROB and MHB             | 103 |

|   | 5.5   | Trade  | off Analysis                                                    | 104 |

|   |       | 5.5.1  | Architectural vs Future Main Memory                             | 104 |

|   |       | 5.5.2  | Single vs Multiple Speculative Tasks & Versions per Processor   | 107 |

|   |       | 5.5.3  | Eager vs Lazy Merging with Main Memory State                    | 109 |

|   | 5.6   | Evalua | ation Methodology                                               | 113 |

|   |       | 5.6.1  | Simulation Environment                                          | 113 |

|   |       | 5.6.2  | Applications                                                    | 114 |

|   | 5.7   | Evalua | ation                                                           | 116 |

|   |       | 5.7.1  | Single vs Multiple Speculative Tasks/Versions per Processor     | 116 |

|   |       | 5.7.2  | Eager vs Lazy Merging with Main Memory State                    | 117 |

|   |       | 5.7.3  | Architectural vs Future Main Memory System                      | 119 |

|   |       | 5.7.4  | Summary                                                         | 121 |

|   | 5.8   | Conclu | usion                                                           | 121 |

| 6 | Soft  | ward 1 | Buffering Under Speculative Thread-Level Parallelization        | 127 |

| - | ~ 511 |        | onder operative in edd never i didienzation                     |     |

|            | 6.1  | $\operatorname{Introd}$ | uction                                                      | . 127       |

|------------|------|-------------------------|-------------------------------------------------------------|-------------|

|            | 6.2  | Specul                  | lation Protocol Used                                        | . 129       |

|            | 6.3  | Overv                   | iew of the History Buffer Operation                         | . 130       |

|            | 6.4  | Efficie                 | nt Software Implementation                                  | . 131       |

|            |      | 6.4.1                   | Accessing Local Task-IDs in Software                        | . 132       |

|            |      | 6.4.2                   | Caching Task-IDs                                            | . 134       |

|            |      | 6.4.3                   | Quantifying Insertion Overhead                              | . 134       |

|            |      | 6.4.4                   | Filtering the First Store                                   | . 136       |

|            |      | 6.4.5                   | Exposed Loads that Need to Be Buffered                      | . 139       |

|            |      | 6.4.6                   | Other Issues                                                | . 140       |

|            |      | 6.4.7                   | Correct Interleaving                                        | . 141       |

|            |      | 6.4.8                   | Hardware-Intensive Solution                                 | . 143       |

|            | 6.5  | Evalua                  | ation Methodology                                           | . 144       |

|            |      | 6.5.1                   | Simulation Environment                                      | . 144       |

|            |      | 6.5.2                   | Applications                                                | . 145       |

|            | 6.6  | Evalua                  | ation                                                       | . 146       |

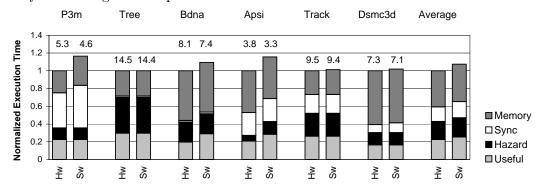

|            |      | 6.6.1                   | Impact of Software Buffering on Execution Time              | . 147       |

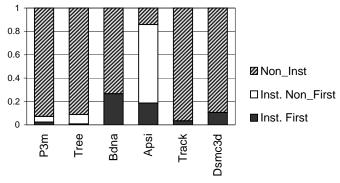

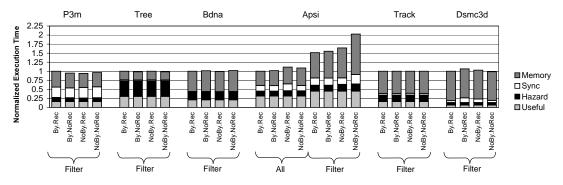

|            |      | 6.6.2                   | Implementation Overheads of Advanced Buffering              | . 148       |

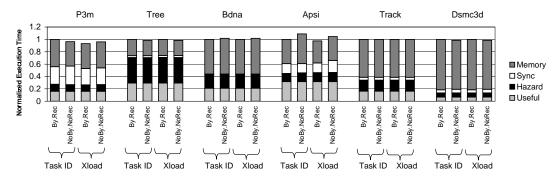

|            |      | 6.6.3                   | Alternative Designs for Software Logging                    | . 150       |

|            | 6.7  | Summ                    | ary                                                         | . 154       |

| 7          | Con  | clusio                  | ns and Future Work                                          | 157         |

|            | 7.1  | Conclu                  | isions                                                      | . 157       |

|            |      | 7.1.1                   | Hardware Prefetch                                           | . 157       |

|            |      | 7.1.2                   | Parallelizing Reductions                                    | . 159       |

|            |      | 7.1.3                   | State Buffering in Speculative Thread-Level Parallelization | . 160       |

|            | 7.2  | Future                  | e Work                                                      | . 161       |

| ۱,         | ppen | dix A:                  | Speculation Protocol for MultiT&MV lazy FMM systems         | 163         |

|            |      |                         |                                                             | . <b></b> . |

| <b>1</b> ] | ppen | dix B:                  | Description of the Applications                             | 175         |

| Appendix C: Example of Poor MultiT&SV Performance | 177 |

|---------------------------------------------------|-----|

| References                                        | 179 |

## List of Figures

| 2.1  | Sparse vector.                                                                | 21 |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | Sparse vector stored using the LL format                                      | 21 |

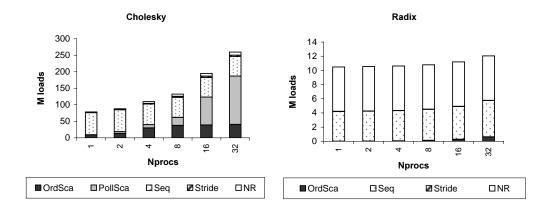

| 2.3  | Breakdown of pattern distribution for 16 processors                           | 24 |

| 2.4  | Breakdown of pattern distribution for Cholesky and Radix (1-32 processors)    | 25 |

| 2.5  | Effect of removing the first three loads of each sequence                     | 27 |

| 2.6  | Changes in sequence length with the number of processors                      | 29 |

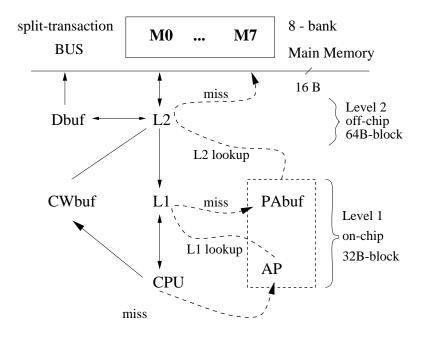

| 3.1  | Base system used for comparing prefetching techniques                         | 38 |

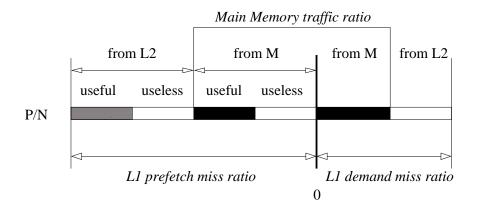

| 3.2  | Performance mode. Demand and prefetch miss ratios are shown                   | 41 |

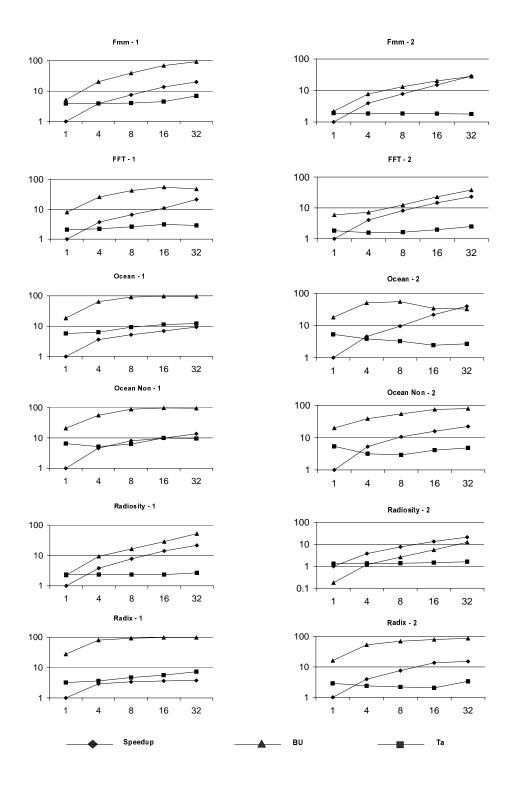

| 3.3  | Speedup, Ta and BU vs. number of processors, for the Base system              | 43 |

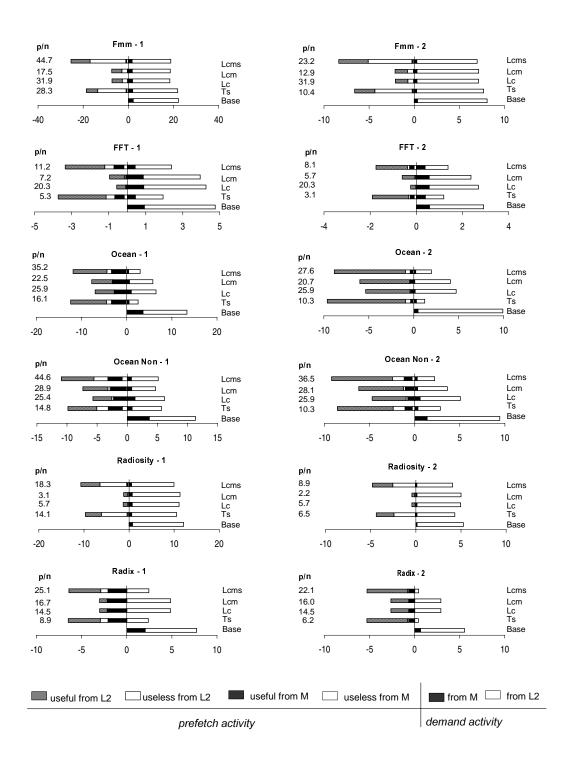

| 3.4  | Demand and prefetch miss ratios                                               | 45 |

| 4.1  | Loop with anti and flow dependences                                           | 55 |

| 4.2  | Loop with a reduction operation                                               | 56 |

| 4.3  | Code resulting from parallelizing the loop in Figure 4.2                      | 57 |

| 4.4  | Representation of how PCLR works                                              | 59 |

| 4.5  | Parallelized reduction code under PCLR                                        | 60 |

| 4.6  | Code using a swap instruction to solve the atomicity problem                  | 65 |

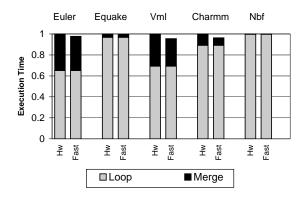

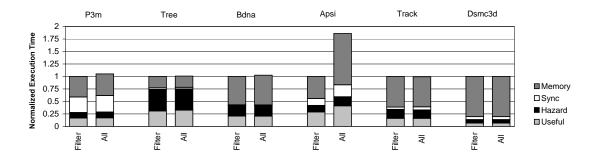

| 4.7  | Execution time under different schemes for a 16-node multiprocessor $\dots$   | 70 |

| 4.8  | Speedups delivered by the different mechanisms (harmonic mean)                | 72 |

| 4.9  | Comparing the performance with floating-point units of different frequencies. | 73 |

| 4.10 | Loop to be parallelized with privatization and dynamic last value assign-     |    |

|      | ment                                                                          | 74 |

| 4.11 | Code resulting from parallelizing the loop in Figure 4.10 with dynamic last value assignment                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.12 | Parallelized reduction code with dynamic last value assignment under PCLR                                                                       |

|      | PCLR                                                                                                                                            |

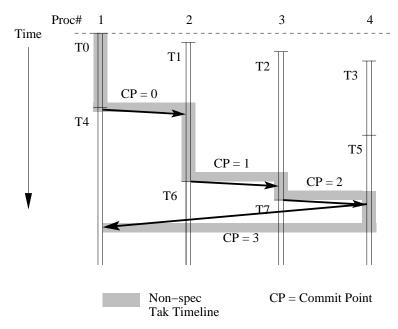

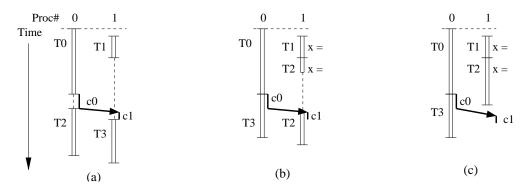

| 5.1  | Several tasks executing under speculative execution                                                                                             |

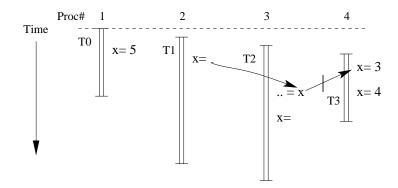

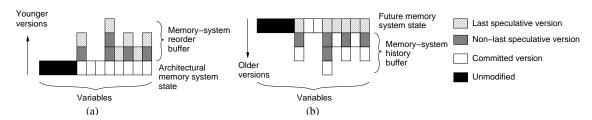

| 5.2  | Multiple versions of the same variable in the system                                                                                            |

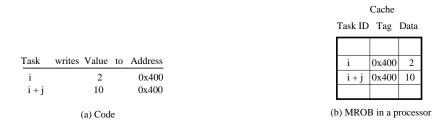

| 5.3  | Cache keeping versions of different tasks and addresses                                                                                         |

| 5.4  | Multiple local speculative versions. Last versions and non-last versions $90$                                                                   |

| 5.5  | Examples of non-analyzable loops with mostly-privatization access patterns 92                                                                   |

| 5.6  | Speculative State Composition                                                                                                                   |

| 5.7  | Taxonomy of approaches to manage multi-version speculative state 94                                                                             |

| 5.8  | Mapping schemes for speculative parallelization onto our taxonomy 96                                                                            |

| 5.9  | Implementing a distributed MROB                                                                                                                 |

| 5.10 | Data structure organization where non-last versions are remapped 101                                                                            |

| 5.11 | Implementing a Distributed MHB                                                                                                                  |

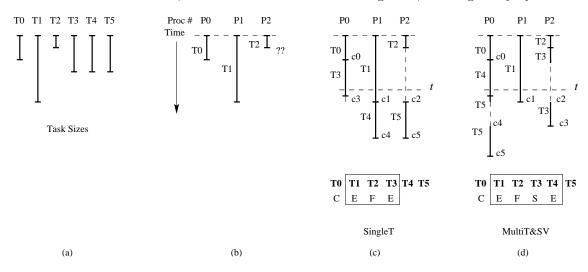

| 5.12 | Example of tasks executing under SingleT, MultiT&SV, and MultiT&MV . $108$                                                                      |

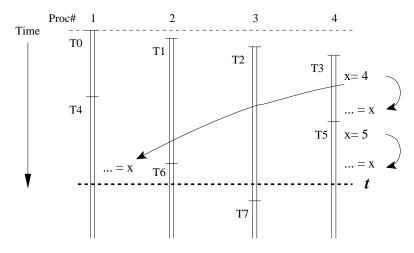

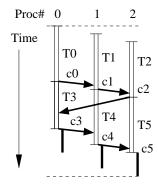

| 5.13 | Progress of the execution and commit wavefronts for a lazy AMM/FMM                                                                              |

|      | system                                                                                                                                          |

| 5.14 | Progress of the execution and commit wavefronts in different schemes: eager AMM, lazy AMM with stalls, eager AMM with stalls, and eager FMM 110 |

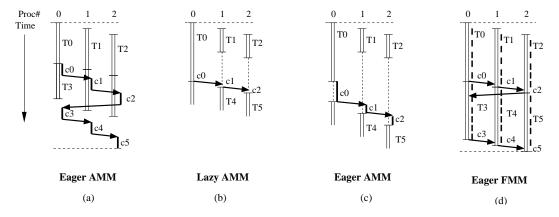

| 5.15 | Application characteristics that limit performance in each approach 112                                                                         |

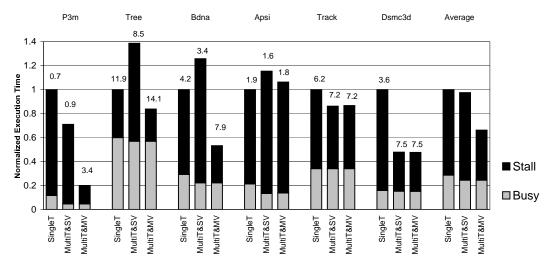

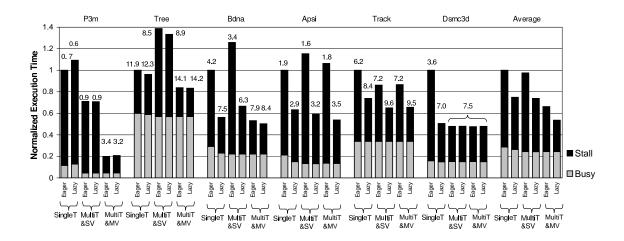

| 5.16 | Effect of supporting single or multiple speculative tasks or versions per processor                                                             |

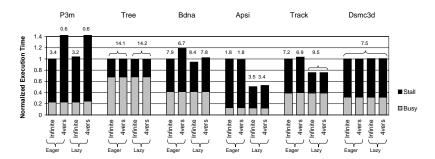

| 5.17 | Effect of supporting eager or lazy merging with main memory state 118                                                                           |

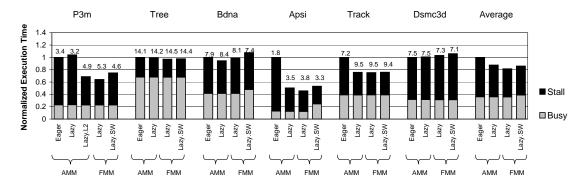

|      | Effect of limited support for eager or lazy merging with main memory state. 119                                                                 |

|      | Effect of supporting an architectural or a future main memory system 120                                                                        |

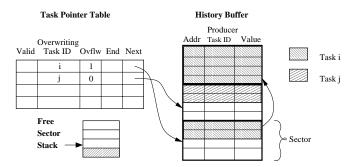

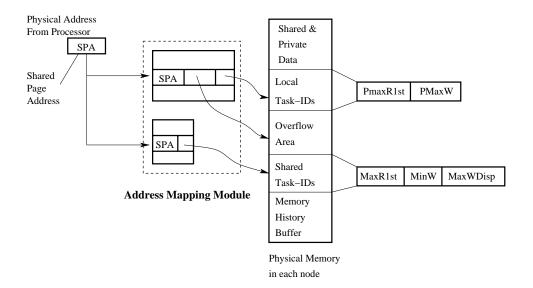

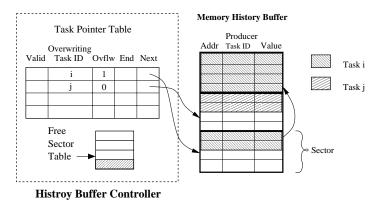

| 6.1  | Per-processor structures that we use for the history buffer                                                                                     |

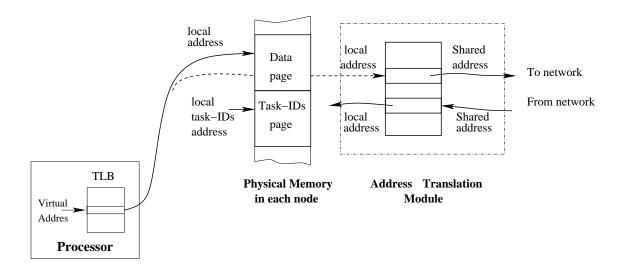

| 6.2  | Special mapping to access task-IDs from software and Address Translation  Module                                                                |

| 63   | Instructions added before a speculative store                                                                                                   |

| 6.4  | Stores to the array B are non-speculative but need to be buffered 136                |

|------|--------------------------------------------------------------------------------------|

| 6.5  | Filtering first stores                                                               |

| 6.6  | Eliminating the branches with the use of predication                                 |

| 6.7  | Example that may result in incorrectly-buffered information                          |

| 6.8  | Execution time under different schemes for a 16-node multiprocessor 147              |

| 6.9  | Breakdown of dynamic stores                                                          |

| 6.10 | Effect of eliminating first-store filtering                                          |

| 6.11 | Effect of log recycling and L1 cache bypassing for logs                              |

| 6.12 | Comparing filtering with task IDs to filtering with extended loads 153               |

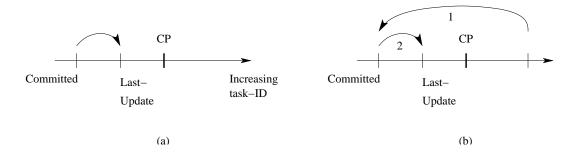

| 7.1  | Sliding commit of Tasks                                                              |

| 7.2  | Address Mapping Module                                                               |

| 7.3  | Per-processor structures required for the Memory History Buffer 167                  |

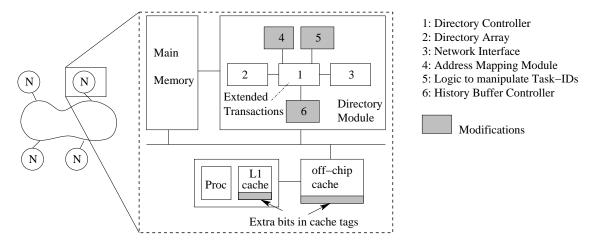

| 7.4  | Modifications required in a DSM machine to support the complete speculation protocol |

| 7.5  | Local and Home algorithm for the speculation protocol 169                            |

| 7.6  | Recovery in an out-of-order RAW dependence infraction                                |

| 7.7  | Example where MultiT&SV is slower than SingleT                                       |

## List of Tables

| 2.1 | Access patterns description                                               | 22  |

|-----|---------------------------------------------------------------------------|-----|

| 2.2 | Evaluated subset of SPLASH-2                                              | 23  |

| 2.3 | Dominant sequence length for different access patterns                    | 28  |

| 3.1 | Basic parameters                                                          | 39  |

| 3.2 | Selected cache sizes                                                      | 40  |

| 3.3 | L1 demand miss ratios of loads for the Base system                        | 44  |

| 3.4 | Speedups of LCm and LCms and Ts relative to the Base System               | 47  |

| 4.1 | Architectural characteristics of the modelled CC-NUMA                     | 67  |

| 4.2 | Application characteristics                                               | 68  |

| 4.3 | Lines flushed or displaced in loops with reduction statements             | 71  |

| 5.1 | Application characteristics that illustrate the difficulties of buffering | 91  |

| 5.2 | Application characteristics                                               | 115 |

| 5.3 | Qualitative characteristics of the Applications                           | 116 |

| 6.1 | Applications characteristics                                              | 146 |

| 6.2 | History buffer statistics                                                 | 149 |

| 6.3 | Effect of task IDs loads on the L1 miss rate                              | 150 |

| 7.1 | How to handle dependences between tasks.                                  | 171 |

### Chapter 1

## Introduction

The context that embraces all the research presented in this thesis is **Cache-Coherent** Shared Memory Multiprocessors.

"Multis are a new class of computers based on multiple microprocessors. The small size, low cost, and high performance of microprocessors allow design and construction of computer structures that offer significant advantages in manufacture, price-performance ratio, and reliability over traditional computer families ... Multis are likely to be the basis for the next, the fith, generation of computers" [Bel85].

#### 1.1 Motivation

Shared Memory Multiprocessors offer the programmer a single memory address space that all the processors share. Processors communicate through shared variables in memory, with all processors capable of accessing any memory location via loads and stores. With shared memory, since processors operate in parallel they need to coordinate when accessing shared data. Thus, when sharing is supported with a single address space, a separate mechanism for synchronization is provided. One approach is to use atomic read-modify instructions operating on lock variables. With locks, only a processor can enter the critical section, and the other processors interested in the shared data must wait until the winner processor unlocks the variable.

Shared memory multiprocessors can have two different organizations. In the first one, processors and memory are connected through an indirect interconnection network, typically a shared bus and main memory is physically centralized. In the second one, memory is physically distributed in nodes containing one or more processors, and these nodes are connected through a direct interconnection network, like a mesh or a hypercube. Dis-

tributed memory multiprocessors are usually called DSM (Distributed Shared Memory) machines [NAB+95] or CC-NUMA(Cache-Coherent Non Uniform Memory Access) machines [SJG92]. In this work, we will use the two terms indistinctly. In both organizations caches are used to reduce the memory latency and increase the processor utilization. They are kept coherent by means of coherence protocols: snoopy protocols in the first case, and directory-based protocols in the second one. In the bus-based organization, the bus limits the bandwidth to access the memory. Thus, this organization does not scale as the number of processors increase, unless we use very expensive networks like multistage networks or crossbars. In the second organization, the memory is distributed, and the memory bandwidth grows as the number of nodes increases, which makes this organization to be scalable.

These multiprocessor systems were designed to reduce the execution time of a single application containing parallel threads or tasks. However, up to now the most important use of the multiprocessors has been the execution of a multiprogrammed workload where independent processes execute in parallel instead of time-sharing a single processor. Several reasons can explain why multiprocessors are not very often used to execute parallel programs. The first one is that it is hard to find parallel programs. On one side, parallel programming is not easy. Thus, only a few applications have been re-written so that they can execute in parallel. On the other side, despite the advances in compiler technology, there are still not many codes that the compiler can fully parallelize. The second reason is that, when multiprocessors execute parallel programs, they usually deliver lower speedups than expected. The main cause for this is the additional main-memory accesses that programs running on a multiprocessor require. In addition, a main-memory access in a multiprocessor is typically slower than in a uniprocessor: interconnection networks have additional delays and the machine is physically bigger.

In this thesis, we address these two problems, and propose several extensions or modifications. Our goal is to reduce the execution time of a single application executing in a shared memory multiprocessor. In particular, we have considered hardware prefetch and reduction support for parallelized codes, and speculative execution support for sections of parallel codes that the compiler could not parallelize.

Prefetch is a well known technique that can speed-up a program by preloading data in cache before the processor needs them. Prefetch is only effective if the prefetcher can learn and reproduce in advance the patterns that the program is following when accessing memory. However, there is no systematic study of the data access patterns that appear in parallel programs. In this thesis, we perform that study for a set of relevant patterns. In addition, we measure if the distribution pattern distribution changes as the

number of processors executing the application changes. We use this study as the starting point for designing a low-cost hardware prefetch mechanism for bus-based multiprocessors. Prefetching in this environment is difficult due to the limited bandwidth resources.

The second technique that we have selected to speed-up the execution of parallel programs is to provide architectural support for parallel reductions. We have observed that reduction operations appear in many scientific codes that the compiler can parallelize. Reductions are important and time-consuming operations. However, finding the most appropriate transformation for a given reduction is usually hard. This is even harder in case of sparse, dynamic applications, where the compiler does not usually has knowledge about the data that each processor needs to access. With DSM machines, things become worse, because the latency to access memory is variable, and depends on the data layout. In this context, we propose new architectural supports that speed-up parallel reduction and make them scalable. These supports require small modifications to the directory of a DSM machine.

Finally we consider speculative thread-level parallelization. Using this approach we can extract tasks of sequential codes that the compiler cannot fully analyze, and speculatively execute them in parallel. The multiprocessor is modified with extra hardware to dynamically detect dependences. If the speculative parallel execution is incorrect a combination of hardware and software repairs the state in memory and resume with the parallel execution. In order to be able to repair the corrupted state in memory, the speculative state produced by these parallel tasks needs to be kept. Given the distributed nature of the memory and caches in a multiprocessor, this buffering is challenging. In this thesis we address the problem of buffering speculative memory state in speculative thread-level parallelization for DSM machines.

Note that this work considers two very different, but important, hardware environments. Prefetch is developed for bus-based multiprocessors, while parallel reduction support and speculative state buffering is developed for scalable DSM machines. Many commercial designs follow nowadays the first trend, like the bus-based multiprocessor Sun Enterprise E450 with up to 4 UltraSPARC processors, or the L2000 of HP with up to 4 PA8500 or PA8600 processors. On the other hand, despite their low commercial presence (SGI Origin is the obliged reference), DSM machines seem to be the straightest way to achieve significant speed-ups in applications requiring access to big amounts of shared memory [BC02].

#### 1.1.1 Hardware Prefetch

One of the mechanisms that we propose to increase the multiprocessor performance is the ability to predict the addresses that the processor will issue in the near future. These addresses are used to prefetch data into the levels of the memory hierarchy closer to the processor. A well-managed data prefetching can hide the latency to access memory, and thus speed-up the application.

Data prefetch can be software [KCPT95, MG91, TE95], when either the programmer or the compiler add extra instructions to prefetch data. It can be hardware [DDS93, CC98], when the hardware of the processor is modified to dynamically predict future addresses. Finally, it can also be hybrid [CB94, ZT95] when hardware and software collaborate in the data prefetch.

In this thesis we are interested in hardware mechanisms. These mechanisms were initially proposed for uni-processors. Simple mechanisms are those able to predict sequential accesses [Smi78], or accesses that differ in a constant stride [CB94, FP92]. More complex hardware mechanisms are able to detect the patterns of single loads that access records chained by pointers and 4-bytes elements of an index list [IVBG98, MH96]. Recent proposals, and also in the uniprocessor context, perform a dependence analysis to find a relation between pairs of loads traversing a linked list [RIVL00, RMS98], or correlate a sequence of misses for a particular miss reference address [JG99].

All previous proposals on hardware prefetch mechanisms track the regularity in the address stream issued by the loads that the processor executed in the past, and based in this regularity try to predict the future addresses. Thus, to guide the research of new mechanisms for multiprocessor systems, it is important to know the data access patterns that appear in parallel programs. It is also important to know how the access patterns and its distribution changes as the number of processors executing the application changes. No systematic study on pattern characterization has been done. The work in [DS96] did some, and measured the burst length of certain patterns. However, no study on pattern characterization that took into account the variation in the number of processors was done. We study all these issues in Chapter 2.

On the other hand, little work has been done on hardware prefetch for bus-based multiprocessors. Sequential and stride-based mechanisms have been evaluated in the context of multiprocessors [CB94, DDS93, DS96, DS98]. But in these works processors are connected through a interconnection network, where latency is assumed to be low. Also, results in [DS95, DS96] show that prefetch can increase the traffic significantly, which can become a serious bottleneck in a bus-based multiprocessor where memory bandwidth is

limited. In the context of bus-based multiprocessors, the most important work has been presented in [TE95, TE93]. This work is based on software prefetch, and the evaluation is done for a fixed number of processors.

In Chapter 3 we focus in hardware prefetch mechanisms for bus-based multiprocessors, that are able to detect simple patterns like the sequential and stride one, and more complex ones like single load linked list and index list traversal [IVBG98, MH96]. One of the goals of this research is to correlate the variation in the number of processors with the effectiveness of the prefetch.

#### 1.1.2 Parallelizing Reductions

Reduction operations are frequently found at the core of many scientific applications. A reduction occurs when an associative and commutative operator  $\otimes$  operates on a variable x as in  $x = x \otimes expression$ . x is called the reduction variable, and it can be a scalar or an array element. If the reduction operation is in a loop and certain conditions are satisfied the loop can be parallelized. However, a loop with a reduction operation can have complex flow dependences across iterations, and therefore special transformations are required. Several transformations have been proposed, but it is usually hard to know which of them is the most appropriate to parallelize the loop. The election depends on many parameters like the degree of contention of the reduction element (number of iterations referencing it) or the sparsity (ratio of referenced elements to the dimension of the array) that can only be known at run-time. In addition, many of these transformations do not scale as the number of processors increases.

For low-contention reductions, a common used mechanism is to enclose the access to the reduction variable in an unordered critical section [EHLP91, Zim91], or with an atomic fetch-and-op operation. The main drawback of this method is that it is not scalable, as the contention for the critical section increases with the number of processors.

Another mechanism that has been used to parallelize reductions is based on the use of inspector-executor loops. An approach based on this inspector-executor mechanism is GatherScatter [DUSH94]. With the GatherScatter approach an inspector loop identifies non-local data needed by each processor, and generates a communication schedule. Then, a executor loop uses the communication schedule to gather nonlocal data, perform the computation using local buffers, and scatters non local results to the appropriate processors. Another different approach also based in the inspector-executor is LocalWrite [HH98]. With LocalWrite the computation partitioning is done so that each processor only computes new values for locally owned data. By writing only to local data, LocalWrite avoids the overhead of mapping nonlocal indices into local buffers (i.e. address translations), or

mutual exclusion synchronization; however, LocalWrite must replicate computation when an iteration writes to data placed in different nodes. In addition, both approaches incur the overhead of executing the inspector loop. Usually, this overhead is amortized if the loop is executed several times, but when the loop is adaptive the inspector has to be executed every time that the access pattern changes.

Finally, another approach to parallelize reductions is to exploit the fact that a reduction is a commutative and associative recurrence, and thus it can be parallelized using a recursive doubling algorithm [Kru86, Lei92]. Several implementations of this method have been proposed [Pot97, LP98]. One of them is the Replicated Private Arrays. In this implementation, the reduction variable is privatized using replicated arrays in all the processors, and the partial results are accumulated on each processor. After the parallel loop finishes, results from the replicated arrays are combined in a final merge step. This merge step is usually implemented with a cross-processor algorithm, that suffers from many remote misses. In addition, the execution time of this merge step is proportional to the size of the array, and does not decrease when more processors are used. Some approaches try to reduce the execution time of this merging phase by using a hash table when accumulating partial results; however, then the overhead is displaced to the main computation loop, because an indirect access is needed to access the appropriate entry in the hash table. Some researchers like [YR00] have developed an algorithm to characterize at run-time the reduction access pattern and choose the most appropriate parallelizing mechanism. However, as the inspector-executor mechanism, their mechanism also incurs some extra overheads that can only be amortized if the reduction access pattern does not change across loop invocations.

Thus, since reduction operations are very important and account for a large fraction of the execution time of many scientific applications, in Chapter 4 we investigate on new architectural support to speed-up parallel execution of reduction operations, and to make them scalable. This support should significantly speed-up execution of irregular and adaptive reduction, overcoming the situations where the software transformations did not succeed. I order to use commodity processors, we will always avoid or minimize changes in the processor, and concentrate the changes in the network/directory coherence controller of the DSM multiprocessor.

#### 1.1.3 State Buffering in Speculative Thread-Level Parallelization

Despite the advances in compiler technology [BDE<sup>+</sup>96, HAA<sup>+</sup>96, SSC<sup>+</sup>99], there are still many codes that cannot be successfully parallelized. These are codes that have complex access patterns, like codes with subscripts of subscripts array accesses, pointers, complex

function calls, or input-dependent access patterns. In these cases, the compiler cannot safely parallelize these code sections, and they have to be executed serially. However, if these codes could be executed in parallel a significant degree of parallelism could be extracted.

To solve this problem, some work propose software solutions like the inspector-executor mechanism [CTY94, RP94, ZY87]. In this approach an inspector loop executes first. This loop gathers the data dependence structure of the code. This information will be used by the executor loop to execute the loop with explicit synchronizations to guarantee correct execution. Other software solutions [GN98, RP99] assume that there are not dependences and speculatively execute the code in parallel at the same time that collect the data accessed at run time. When the code ends, there is a test to determine if the parallel execution was correct or incorrect. If it was incorrect, the code must execute again in parallel. While all these techniques are promising they all have some drawbacks that limit their scalability.

Hardware based approaches assume that there are not dependences and let the compiler to extract tasks and execute them in parallel [CMT00, FF01, GVSS98, HWO98, Kni86, KT99, MGT98, OWP+01, PGRT01, SBV95, SCZM00, THA+99, ZRT99]. These schemes extend the invalidation-based cache coherence of the processor and check for dependences at run-time. In case of a violation, a combination of hardware and software solves it. This usually requires the squash of the tasks, the repair of the corrupted memory state and the re-start of the tasks in parallel. These mechanisms have been proposed at the chip-level multiprocessor [GVSS98, HWO98, KT99, MGT98, OWP+01, SBV95, THA+99] or at more scalable levels like [CMT00, FF01, GN98, PGRT01, RP95, RS00, SCZM00, ZRT99].

In Chapter 5, we will focus on the study of mechanisms to buffer the speculative state during speculative thread-level parallelization. Different approaches handle this issue differently. Some times this speculative state is buffered in the write-buffers of the processor [HWO98, THA<sup>+</sup>99], caches [CMT00, FF01, GVSS98, KT99, OWP<sup>+</sup>01, SCZM00], or special buffers [FS96, PGRT01] to avoid corrupting main memory. Other proposals take a different approach and generate a log of updates that allows them to backtrack execution [FLA01, Zha99, ZRT99]. Often, there are differences in the way caches, buffers and logs are used in the different schemes. However, there is no study that breaks down the design space and identifies the major design decisions and tradeoffs, and provides a performance and complexity comparison of important design points. We feel that such a study is needed, specially given the high performance that stakes of choosing a particular buffering scheme.

In addition, in this context of speculative thread-level parallelization, we also explore

new buffering mechanisms. In particular, we are interested on the problem of keeping multiple versions of the same variable. This problem appears when several tasks run in a processor and remain speculative. In this case the processor has to buffer the state that all these tasks produced. If these tasks wrote to different variables, then the processor must keep different versions of the same variable. All the current proposals that handle this problem require non-negligible modifications and additional hardware. Thus, in Chapter 6 we explore software algorithms to implement an efficient multi-version buffering scheme. We evaluate the overheads that the software introduced, and which are the performance benefits that this mechanism can deliver.

#### 1.2 Thesis Contributions

This work makes several contributions in the context of shared memory multiprocessors. The first contribution is the characterization of the data access patterns in parallel programs. We perform a systematic characterization of the applications, and we study for first time the change in the program behaviour (pattern distribution and sequence length) as the number of processors increases. Also, in the context of multiprocessors, we propose a new performance model that facilitates the analysis of the demand and prefetch missrations, and traffic between caches, and with main memory. We evaluate several hardware prefetch mechanisms for a bus-based multiprocessor system, and we propose a new one. Our proposed mechanism combine a Load Cache with an on-miss insertion policy plus a sequential mechanism. Since bus-based multiprocessors have a limited bandwidth, we propose that the sequential prefetcher can be connected or disconnected. This decision can be taken by either the programmer or the compiler depending on the number of processors executing the application, and the behaviour of the application.

The second contribution of this thesis is the design and evaluation of architectural support for parallel reductions. The idea is to use the caches of the processors as temporary storage where processors accumulate their partial results. As cache lines are displaced, their values are combined with the value in the shared memory location. The required architectural changes are mostly confined to the directory controllers. Our design includes naive hardware modifications to detect reduction accesses, as well as a more advance scheme where the use of extra shadow addresses and the addition of operating system support avoids modifications of the processor. It also identifies the atomicity problems that appears, discuss the main tradeoffs of the different types of solutions, and propose two solutions. Finally we present a scenario of dynamic last value assignment where this architectural support can also be used. The proposed support speeds-ups significantly parallel reductions and makes them scalable when executing in shared-memory multiprocessors.

The third contribution of the thesis is related with the buffering of state in speculative thread-level parallelization. In this context, this thesis presents a novel taxonomy of the different approaches to handle speculative state. Our taxonomy includes a novel application of the concepts of architectural and future state to the memory state. It also classifies the approaches based on the support for multiple tasks and versions, and the main memory update policy. We perform a detailed tradeoff analysis and evaluate all the different approaches under a single architectural framework. We characterize a set of applications that are candidate for speculative thread-level parallelization. Our key insights are useful to understand the main bottlenecks of speculative thread-level systems based on the application characteristics.

Finally, for a particular type of approaches, we propose an effective software scheme to buffer multi-version speculative state. For that, we take a speculative parallelization protocol, and build all the software implementation of the buffering scheme on top of it. We evaluate the performance of our proposed only-software scheme, and compare it to a similar only-hardware one. Our study also includes a detailed evaluation of the major issues of our software proposal like the filtering of first stores.

#### 1.3 Thesis Organization

This thesis is organized as follows. Chapter 2 performs a characterization of important data access patterns that appear in parallel applications, and show several interesting metrics which can be applied to evaluate the potential of hardware data prefetch. In Chapter 3 we design and evaluate a low-cost Hardware Prefetch Mechanism for Busbased Multiprocessors. Chapter 4 shows an architectural support added to a Scalable Shared Memory Multiprocessors to speed-up parallel reduction operations and make them scalable. Chapter 5 presents tradeoffs in the Buffering of Speculative State in Speculative Thread-Level Speculation. Chapter 6 presents a software scheme to buffer state from multiple tasks and versions, and finally Chapter 7 summarizes and presents future work.

## References

- [BC02] G. Bell and J. Cray. What's Next in High-Performance Computing? Communications of the ACM, 45(2):91–95, February 2002.

- [BDE+96] W. Blume, R. Doallo, R. Eigenmann, J. Grout, J. Hoeflinger, T. Lawrence, J. Lee, D. Padua, Y. Paek, B. Pottenger, L. Rauchwerger, and P. Tu. Advanced Program Restructuring for High-Performance Computers with Polaris. *IEEE Computer*, 29(12):78-82, December 1996.

- [Bel85] C. G. Bell. Multis: A New Class of Multiprocessor Computers. *Science*, 228:462–467, April 1985.

- [CB94] T.F. Chen and J.L. Baer. A Performance Study of Software and Hardware Data Prefetching Schemes. In *Proc. of the 21st Annual Int'l Symposium on Computer Architecture (ISCA'94)*, pages 223–232, April 1994.

- [CC98] C.H. Chi and C.M. Cheung. Hardware Prefetching for Pointer Data References. In Proc. of the 1998 Int'l Conference on Supercomputing (ICS'98), pages 377–384, 1998.

- [CMT00] M. Cintra, J. F. Martínez, and J. Torrellas. Architectural Support for Scalable Speculative Parallelization in Shared-Memory Multiprocessors. In *Proc. of the 27th Annual Int'l Symposium on Computer Architecture (ISCA '00)*, pages 13–24, June 2000.

- [CTY94] D. K. Chen, J. Torrellas, and P. C. Yew. An Efficient Algorithm for the Run-Time Parallelization of Do-Across Loops. In In Proc. of Supercomputing '1994, pages 518–527, November 1994.

- [DDS93] F. Dahlgren, M. Dubois, and P. Stenström. Fixed and Adaptive Sequential Prefetching in Shared Memory Multiprocessors. In 1993 Int'l Conference on Parallel Processing (ICPP'93), volume 1, pages 56–63, August 1993.

- [DS95] F. Dahlgren and P. Stenström. Effectiveness of Hardware-based Stride and Sequential Prefetching in Shared-Memory Multiprocessors. In *Proc. of the 1st Int'l Symposium on High-Performance Computer Architecture (HPCA '95)*, pages 68–77, January 1995.

- [DS96] F. Dahlgren and P. Stenström. Evaluation of Hardware-Based Stride and Sequential Prefetching in Shared Memory Multiprocessors. *IEEE Trans. on Parallel and Distributed Systems*, 7(4):385–398, April 1996.

- [DS98] F. Dahlgren and P. Stenström. Performance Evaluation and Cost Analysis of Cache Protocol Extensions for Shared-Memory Multiprocessors. *IEEE Trans. on Computers*, 47(18):385–398, October 1998.

- [DUSH94] R. Das, M. Uysal, J. Saltz, and Y.S. Hwang. Communication Optimizations for Irregular Scientific Computations on Distributed Memory Architectures. *Journal of Parallel and Distributed Computing*, 22(3):462–479, September 1994.

- [EHLP91] R. Eigenmann, J. Hoeflinger, Z. Li, and D. Padua. Experience in the Automatic Parallelization of Four Perfect-Benchmark Programs. Lecture Notes in Computer Science 589. Proceedings of the 4th Workshop on Languages and Compilers for Parallel Computing, Santa Clara, CA, pages 65–83, August 1991.

- [FF01] R. Figueiredo and J. Fortes. Hardware Support for Extracting Coarse-grain Speculative Parallelism in Distributed Shared-memory Multiprocesors. In *Proc. of the Int'l Conference on Parallel Processing (ICPP'01)*, September 2001.

- [FLA01] M. Frank, W. Lee, and S. Amarasinghe. A Software Framework for Supporting General Purpose Applications on Raw Computation Fabrics. Technical Report MIT/LCS Technical Memo 619, July 2001.

- [FP92] J.W.C. Fu and J.H. Patel. Stride Directed Prefetching in Scalar Processors. In *Proc. of the 25th MICRO*, pages 102–110, 1992.

- [FS96] M. Franklin and G. S. Sohi. ARB: A Hardware Mechanism for Dynamic Reordering of Memory References. *IEEE Trans. on Computers*, 45(5):552–571, May 1996.

- [GN98] M. Gupta and R. Nim. Techniques for Speculative Run-Time Parallelization of Loops. In *Proc. of Supercomputing '1998*, November 1998.

- [GVSS98] S. Gopal, T. N. Vijaykumar, J. E. Smith, and G. S. Sohi. Speculative Versioning Cache. In Proc. of the 4th Int'l Symposium on High-Performance Computer Architecture (HPCA'98), pages 195–205, February 1998.

- [HAA+96] M. Hall, J. Anderson, S. Amarasinghe, B. Murphy, S.-W. Liao, E. Bugnion, and M. Lam. Maximizing Multiprocessor Performance with the SUIF Compiler. *IEEE Computer*, 29(12):84–89, December 1996.

- [HH98] C. Tseng H. Han. Improving Compiler and Run-Time Support for Adaptive Irregular Codes. In *Proc. of the Int'l Conference on Parallel Architectures and Compilation Techniques (PACT'98)*, October 1998.

- [HWO98] L. Hammond, M. Willey, and K. Olukotun. Data Speculation Support for a Chip Multiprocessor. In In Proc. of the 8th Int'l Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS'98), pages 58-69, October 1998.

- [IVBG98] P. Ibáñez, V. Viñals, J.L. Briz, and M.J. Garzarán. Characterization and Improvement of Load/Store Cache-Based Prefetching. In Proc. of the 1998 Int'l Conference on Supercomputing (ICS'98), pages 369-376, 1998.

- [JG99] D. Joseph and D. Grundwald. Prefetching using Markov Predictors. *IEEE Trans. on Computers*, 48(2):121–133, February 1999.

- [KCPT95] D. Koufaty, X. Chen, D. Poulsen, and J. Torrellas. Data Forwarding in Scalable Shared-Memory Multiprocessors. In *IEEE Trans. on Parallel and Distributed Systems*, pages 1250–1264, December 1996. A shorter version appeared in Proc. of the 9th Int'l Conference on Supercomputing (ICS'95), pages 255-264, July 1995.

- [Kni86] T. Knight. An Architecture for Mostly Functional Languages. In *ACM Lisp* and Functional Programming Conference, pages 500–519, August 1986.

- [Kru86] C. Kruskal. Efficient Parallel Algorithms for Graph Problems. In Proc. of the 1986 Int'l Conference on Parallel Processing (ICPP'86), pages 869–876, August 1986.

- [KT99] V. Krishnan and J. Torrellas. A Chip-Multiprocessor Architecture with Speculative Multithreading. *IEEE Trans. on Computers, Special Issue on Multithreaded Architectures*, pages 866–880, September 1999.

- [Lei92] F.T. Leighton. Introduction to Parallel Algorithms and Architectures: Arrays, Trees, Hypercubes. Morgan Kaufmann, 1992.

- [LP98] Y. Lin and D. Padua. On the Automatic Parallelization of Sparse and Irregular Fortran Programs. In *Proc. of the Fourth Workshop on Languages, Compilers, and Run-time Systems for Scalable Computers (LCR98)*, 1998.

- [MG91] T. Mowry and A. Gupta. Tolerating Latency through Software-Controlled Prefetching in Shared-Memory Multiprocessors. *Journal of Parallel and Distributed Computing*, 12(2):87–106, June 1991.

- [MGT98] P. Marcuello, A. González, and J. Tubella. Speculative Multithreaded Processors. In Proc. of the 1998 Int'l Conference on Supercomputing (ICS'98), pages 77–84, July 1998.

- [MH96] S. Mehrotra and L. Harrison. Examination of a Memory Access Classification Scheme for Pointer-Intensive and Numeric Programs. In Proc. of the 1996 Int'l Conference on Supercomputing (ICS'96), pages 133–143, 1996.

- [NAB+95] A. Nowatzyk, G. Aybay, M. Browne, E. Kelly, M. Parkin, B. Radke, and S. Vishin. The S3.mp Scalable Shared Memory Multiprocessor. In Proc. of the 1995 Int'l Conference on Parallel Processing (ICPP'95), pages 1–10, August 1995.

- [OWP+01] C.L. Ooi, S. Wook, K.I. Park, R. Eigenmann, B. Falsafi, and T.N. Vijaykumar. Multiplex: Unifying Conventional and Speculative Thread-Level Parallelism on a Chip Multiprocessor. In Proc. of the 2001 Int'l Conference on Supercomputing (ICS'01), June 2001.

- [PGRT01] M. Prvulovic, M. J. Garzarán, L. Rauchwerger, and J. Torrellas. Removing Architectural Bottlenecks to the Scalability of Speculative Parallelization. In *Proc. of the 28th Annual Int'l Symposium on Computer Architecture* (ISCA '01), pages 204–215, July 2001.

- [Pot97] W.M. Pottenger. Theory, Techniques, and Experiments in Solving Recurrences in Computer Programs. Technical Report, University of Illinois at Urbana-Champaign, Center for Supercomputing Research and Developement, May 1997.

- [RIVL00] L. Ramos, P. Ibáñez, V. Viñals, and J.M. Llabería. Modeling Load Address Behaviour Through Recurrences. In Proc. of the 2000 Int'l Symposium on Performance Analysis of Systems and Software (ISPASS'00), pages 101–108, April 2000.

- [RMS98] A. Roth, A. Moshovos, and G.S. Sohi. Dependence Based Prefetching for Linked Data Structures. In Proc. of the 8th Int'l Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS'98), pages 115–126, October 1998.

- [RP94] L. Rauchwerger and D. Padua. The PRIVATIZING DOALL Test: A Run-Time Technique for DOALL Loop Identification and Array Privatization. In Proc. of the 1994 Int'l Conference on Supercomputing (ICS'94), pages 33–43, July 1994.

- [RP95] L. Rauchwerger and D. Padua. The LRPD Test: Speculative Run-Time Parallelization of Loops with Privatization and Reduction Parallelization. In Proc. of the SIGPLAN 1995 Conference on Programming Language Design and Implementation (PLDI'95), pages 218–232, June 1995.

- [RP99] L. Rauchwerger and D. Padua. The LRPD Test: Speculative Run-Time Parallelization of Loops with Privatization and Reduction Parallelization. IEEE Trans. on Parallel and Distributed Systems, 10(2), 1999.

- [RS00] P. Rundberg and P. Stenstrom. Low-Cost Thread-Level Data Dependence Speculation on Multiprocessors. In Fourth Workshop on Multithreaded Execution, Architecture and Compilation, December 2000.

- [SBV95] G. S. Sohi, S. Breach, and S. Vajapeyam. Multiscalar Processors. In *Proc. of the 22nd Annual Int'l Symposium on Computer Architecture (ISCA'95)*, pages 414–425, June 1995.

- [SCZM00] J.G. Steffan, C.B. Colohan, A. Zhai, and T. C. Mowry. A Scalable Approach to Thread-Level Speculation. In *Proc. of the 27th Annual Int'l Symposium on Computer Architecture (ISCA '00)*, pages 1–12, June 2000.

- [SJG92] P. Stenstrom, T. Joe, and A. Gupta. Comparative Performance Evaluation of Cache-Coherent NUMA and COMA Architectures. In *Proc. of the 19th Annual Int'l Symp. on Computer Architecture (ISCA'92)*, pages 80–91, 1992.

- [Smi78] Alan Jay Smith. Sequential Program Prefetching in Memory Hierarchies.  $IEEE\ Computer,\ 11(12):7-21,\ December\ 1978.$

- [SSC+99] H. Saito, N. Stavrakos, S. Carrol, C. Polychronopoulos, and A. Nicolau. The Design of the PROMIS Compiler. In Proc. of the Int'l Conference on Compiler Construction, pages 562-573, March 1999.

- [TE93] D.M. Tullsen and S.J. Eggers. Limitations of Cache Prefetching on a Bus-Based Multiprocessor. In *Proc. of the 20th Annual Int'l Symposium on Computer Architecture (ISCA '93)*, pages 278–288, may 1993.

- [TE95] D.M. Tullsen and S.J. Eggers. Effective Cache Prefetching on Bus-Based Multiprocessors. ACM Trans. on Computer Systems, 13(1):57–58, February 1995.

- [THA<sup>+</sup>99] J.Y. Tsai, J. Huang, C. Amlo, D. Lilja, and P.C.Yew. The Superthreaded Processor Architecture. *IEEE Trans. on Computers, Special Issue on Multi*threaded Architectures, 48(9):881–902, September 1999.

- [YR00] H. Yu and L. Rauchwerger. Adaptive Reduction Parallelization. In *Proc. of the 2000 Int'l Conference on Supercomputing (ICS'00)*, May 2000.

- [Zha99] Y. Zhang. Hardware for Speculative Parallelization in DSM Multiprocessors. Ph.D. Thesis, University of Illinois at Urbana-Champaign, Department of Electrical and Computer Engineering, May 1999.

- [Zim91] H. Zima. Supercompilers for Parallel and Vector Computers. ACM Press, New York, New York, 1991.

- [ZRT99] Y. Zhang, L. Rauchwerger, and J. Torrellas. Hardware for Speculative Parallelization of Partially-Parallel Loops in DSM Multiprocessors. In *Proceedings of the 5th Int'l Symposium on High-Performance Computer Architecture* (HPCA '99), pages 135–139, January 1999.

- [ZT95] Z. Zhang and J. Torrellas. Speeding up Irregular Applications in Shared-Memory Multiprocessors: Memory Binding and Group Prefetching. In *Proc.* of the 22nd Annual Int'l Symposium on Computer Architecture (ISCA '95), pages 188–199, June 22–24, 1995.

- [ZY87] C.Q. Zhu and P.C. Yew. A Scheme to Enforce Data Dependence on Large Multiprocessor Systems. In IEEE Trans. on Software Engineering, pages 726– 739, June 1987.

## Chapter 2

### Pattern Characterization

Data prefetching has been widely studied as a technique to hide memory access latency in multiprocessors. However, the effectiveness of a prefetch mechanism depends on the regularity in the data access pattern of the program. Characterizing the patterns that appear in the applications is very important, because this information can be very helpful to guide the research of new prefetch mechanisms, and to highlight how a prefetcher should behave for a particular application.

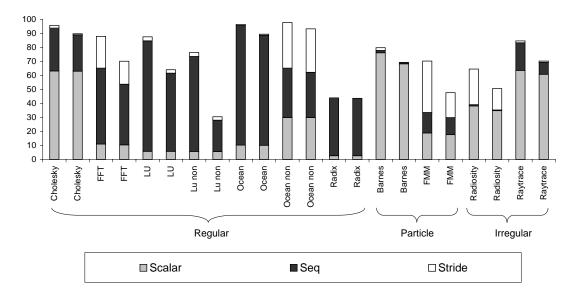

In this chapter we analyze the patterns that appear in a subset of the SPLASH-2 applications. We evaluate the percentage of loads that follow a specific pattern (scalar, sequential, stride, linked list and index list), and the number of times in a row that a load follows a particular pattern (sequence length). We also study the persistence of the patterns and the sequence length as the number of processors executing the application changes from 1 to 32. Our results reveal the dominance of sequential traversals and, to a lesser extent, the presence of stride accesses. We also find that for most of the evaluated applications, with the only exception of Cholesky and Radix, the pattern distribution remains constant independently of the number of processors executing the application. Also the sequence length scarcely changes with the number of processors.

#### 2.1 Introduction

As the processor speed continues to increase, the performance of many applications is limited by the high latency to access memory. If we consider multiprocessors, this latency to access memory is even higher. In a bus-based multiprocessor many processors have to compete for a shared bus, which increases the latency to access memory. In a more scalable multiprocessor where processors are connected through a general network, remote accesses to either main memory or a second processor's cache can take hundreds (300 -

800) of cycles. To cope with this problem a solution that many researchers have explored is data prefetch.

Data prefetching has been proposed to hide read latencies in multiprocessors and uniprocessors. Its effectiveness depends on the regularity in the access pattern of the program, and can be done either in software or in hardware. Software approaches can perform well whenever the programmer or the compiler can provide or extract information about the data access pattern of an application [KCPT95, MG91, TE93]. However, they add extra instructions to the code, and their automatic application may not be easy. Hardware approaches add additional hardware to detect the data access patterns. Based on the detected patterns, they are able to predict the next address that the processor will issue in the near future (e.g. [DS95, DS96, DS98]). In the next chapter, we focus on hardware prefetching mechanisms. In this chapter we characterize the patterns that appear in parallel programs. We only study load access patterns, since write latencies can be easily hidden by the processor. We analyze the percentage of loads that follow one of these five patterns: scalar, sequential, stride, linked list or index list traversal when the traversal of the list is done with a single load, as described in [IVBG98, MH96].

We also study another metric. Hardware prefetch is hardly useful if once a pattern is detected, the pattern does not appear again in the program. For that reason, we have studied the sequence length. The sequence length is the number of times in a row that a load follows a particular pattern. Hardware prefetchers will perform poorly if this number if low. This is due to the learning time they need to get confidence. Furthermore, access patterns or sequence lengths may change when the number of processors executing the application changes. Previous works do not evaluate how this variation on the number of processors executing the application may affect the distribution of the memory access patterns. The length of memory accesses following a given pattern has been measured in [DS96], but little systematic work on pattern characterization has taken into account the number of processors.

In this chapter we use a subset of applications and kernels belonging to the SPLASH-2 suite [WOT<sup>+</sup>95]. We study the data access patterns and the sequence lengths that appear in these applications when the number of processors varies from 1 to 32. Our results reveal the dominance of sequential traversals and, to a lesser extent, the presence of stride accesses. Single load linked list or index list traversal almost does not appear in these applications. We observe small differences in the access pattern distribution or sequence length when the number of processors changes. But for Radix and Cholesky, which are the applications with a higher communication-to-computation ratio, there is a significative change on the access patterns as the number of processors increases. In the

other cases, the sequence length changes relatively little with the number of processors.

This chapter is organized as follows: Section 2.2 presents the patterns measured, the applications evaluated and the environmental setup; Section 2.3 shows the patterns distribution; Section 2.4 studies the sequence length for the different access patterns; Finally Section 2.5 summarizes.

#### 2.2 Measured Patterns and Environmental Setup

The prefetching techniques we use in the next chapter strongly rely on the existence of predictable memory access patterns. As far as we know, there is no systematic study of such patterns in parallel applications as the number of processors varies. Therefore, we have analyzed load accesses for a subset of the SPLASH-2 suite [WOT<sup>+</sup>95], using sequential and non-sequential pattern detectors. We have also analyzed the sequence length of loads. Section 2.2.1 presents these two measured patterns, while Section 2.2.2 presents the experimental setup and the applications we use for our experiments.

#### 2.2.1 Measured Patterns

#### Access Patterns

We have looked for five load patterns which can potentially be recognized by the prefetching techniques we use later. These patterns, which we explain next, have been recognized only when they appear in the stream of addresses issued by a single load.

• Stride (STR) This pattern appears when the distance between the objects accessed is regular and larger than the block size. An example of this pattern appears when traversing the column of a matrix that has been stored in memory by rows.

To detect this pattern we keep track of the addresses issued by each single load during consecutive executions, and we compute the stride S as the difference between these addresses. Thus, we can define:

$$S_i = A_i - A_{i-1},$$

where  $A_i$  and  $A_{i-1}$  are the addresses issued by a load during its i-th and (i-1)-th execution. A pattern is detected when the stride matches the new stride computed the following times that the load executes:

$$S_i = S_{i-1} = S_{i-2} = \dots = S_{i-k},$$

where k is a confidence counter. Once a pattern is detected, the adddres to prefetch can be computed as:

$$A_{i+1} = A_i + S_i$$

We have also considered that a load is accessing memory with a stride pattern when the stride S is negative or larger than the block size.

- Scalar (SCA) This pattern appears when accessing the same address. For instance, when accessing the induction variable in a loop. For hardware prefetch, the detection of this pattern is hardly useful. After the first cache miss the data will be usually in the cache, unless it has been displaced because of cache conflicts or capacity problems. This pattern is a particular case of the stride pattern that is detected when the computed stride S is equal to zero.

- Sequential (SEQ) This pattern appears when accessing objects that are contiguously placed in memory. For instance, stack accesses or accesses to consecutive elements in an array follow this pattern.

This pattern can be considered a particular case of the stride pattern, detected when the stride S is larger than zero and smaller or equal to the block size.

• Linked Data Structure (PTR) This pattern appears when traversing a list of records chained by pointers, where one of the fields of the record is a next pointer to the start address of the next record (e.g. p=p->next).

For the detection of this pattern the value read by the load needs to be tracked. If we call  $d_i$  to the value read by a load during its i-th execution, and  $A_i$  to the address issued also during it i-th execution, we can define  $Desp_i$  as:

$$Desp_i = A_i - d_{i-1}$$

Thus, the linked list pattern is detected when

$$Desp_i = Desp_{i-1} = Desp_{i-2} = \dots = Desp_{i-k}$$

where k is also a confidence counter. The address to prefetch is computed as:

$$A_i = d_i + Desp_i$$

• Index List (IND) This pattern appears in numeric codes and it is a mechanism used by some methods to store vectors or sparse matrix. This pattern is similar to the pointer list, but in this case we have an index vector that stores the index to the next non-zero element of the index vector (e.g. i=index[i], instead of a pointer to the next record).

Figure 2.1 shows the data of a sparse vector. In Figure 2.2, the same vector has been stored using the LL (Linked List) format. With this format, only the non-zero elements of the vector in Figure 2.1 need to be stored in the DATA vector. The COLUMN vector keeps the column where each element of the DATA vector was

placed in the initial vector. The in-order traversal of this vector requires the use of the INDEX vector. The list starts with the element 0. The index to the next non-zero element is in INDEX[0], and is 2. The next index to the next non-zero element is in INDEX[2], and so on.

|      | 0 | 1 | 2 | 3  | 4  | 5 | 6  | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

|------|---|---|---|----|----|---|----|----|---|---|----|----|----|----|----|

| DATA | 0 | 0 | 0 | 71 | 84 | 0 | 86 | 27 | 0 | 0 | 48 | 0  | 0  | 0  | 66 |

Figure 2.1. Sparse vector.

|        | 0  | 1  | 2  | 3  | 4  | 5  |

|--------|----|----|----|----|----|----|

| COLUMN | 3  | 6  | 4  | 10 | 14 | 7  |

| DATA   | 71 | 86 | 84 | 48 | 66 | 27 |

| INDEX  | 2  | 5  | 1  | 4  | -1 | 3  |

Figure 2.2. Sparse vector stored using the LL format.

To detect this pattern we need to compute the initial address of the INDEX vector. We call IV to this address, and Isize to the size of each index (integer) in bytes. We can define  $IV_i$  as:

$$IV_i = A_i - d_{i-1} * Isize$$

Thus, this pattern is detected when

$$IV_i = IV_{i-1} = IV_{i-2} = \dots = IV_{i-k}$$

and the address to prefetch is computed as:

$$A_{i+1} = IV_i + d_i * Isize$$

The mechanism to detect sequential and stride pattern as described here was first proposed in [BC91]. The mechanism to detect linked list and index list traversal was proposed in [MH96].

Table 2.1 summarizes the recurrence conditions explained above for each particular pattern. Remember that we track the stream of addresses issued by a single load. Ai in Table 2.1 is the address generated by a load during its i-th execution, Di is the value read during its i-th execution, and Bsize is the block size [GBIV01]. The first three patterns (SCA, SEQ and STR) are particular cases of regular traversing, characterized by address-address recurrences, whereas the next two (PTR, IND) are value-address recurrences that

we classify as Irregular Traversing. When an instance of a load matches several patterns at a time, it is first classified according to the pattern recognized in the previous instance. If a load follows several patterns at the same time we classify it according to the following priorities: SCA, PTR, IND, STR and SEQ.

| Pat        | Pattern                 |     | Recurrence                                 | Parameter                       |  |

|------------|-------------------------|-----|--------------------------------------------|---------------------------------|--|

| Regular    | $\operatorname{Scalar}$ | SCA | $A_i = A_{i-1}$                            |                                 |  |

| Traversing | Sequential              | SEQ | $A_i = A_{i-1} + \mathbf{s}$               | 0 < s <= Bsize                  |  |

|            | Stride                  |     | $A_i = A_{i-1} + S$                        | $(S > Bsize) \mid \mid (S < 0)$ |  |

|            | Pointer List            | PTR | $A_i = D_{i-1} + d$                        | $record\ displacement = d$      |  |

| Irregular  |                         |     |                                            | index integer size = 4          |  |

| Traversing | Index List              | IND | $A_i = 4*D_{i-1} + K$                      | base address of the             |  |

|            |                         |     |                                            | index array = k                 |  |

| Not Re     | Not Recognized          |     | Not Recognized as any of the previous ones |                                 |  |

**Table 2.1.** The load patterns we consider and the recurrences defining them.  $A_i$  and  $D_i$  refer respectively to the address and value of the i-th instance of a given load instruction.

#### Sequence length

We have also measured sequence lengths. Sequence length is defined as the number of consecutive executions of a load following the same pattern. As an example, the address stream

contains a sequence of length 3, since the 3 bolded addresses differ from the previous ones in the constant stride 64.

Sequence lengths are important because hardware prefetching mechanisms will be useful only if they are long. Hardware prefetching detects that a particular load is accessing memory following a certain pattern by recording the address issued by the load during a minimum number of consecutive times. This is called *learning time* and is used to get confidence. If the load does not execute again once the pattern it follows has been detected, or if it only executes a few times, then the detected pattern will be hardly useful.

In our characterization the minimum length we detect is 2. Thus, the hardware prefetchers we evaluate in the next chapter will need a load to execute 3 times before the first prediction can be issued. If we look at the previous address stream, this means that our hardware prefetcher will use addresses 4 and 68 to compute the stride 64; address 132 will confirm that the load is accessing memory with a stride of 64; then, address 196 will be issued to prefetch.

#### 2.2.2 Workload and Methodology

Table 2.2 shows the selected SPLASH-2 applications and some metrics for 16 processors. The applications have been targeted to a MIPS-2 architecture and run until completion by using MINT, an execution driven simulator for multiprocessors [VF94a]. Throughout the chapter the analysis is constrained to the parallel section of the programs.

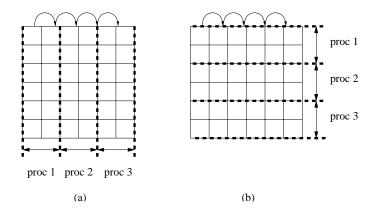

SPLASH-2 programs have been classified into three classes according to the interaction between their data structures and access patterns and the cache lines. We refer to these classes as: a) Regular programs, based on contiguously allocated data structures (Ocean, FFT, LU, Radix and Cholesky), b) Particle programs, based on particles, i.e. structures that can share the same cache line, and that are accessed by different processors (FMM, Barnes); and c) Irregular programs, with highly irregular data structures (Radiosity, Raytrace). The implementations of Ocean and LU used in [VF94b] corresponds to those specified here as Non Contiguous: main data sets are 2-dimensional arrays where sub-blocks are not contiguous in memory. Alternatively, Ocean and LU Contiguous implementations allocate data as arrays of sub-blocks, in order to reduce or even eliminate false sharing. Moreover, in the case of Ocean contiguous, a multi-grid (instead of a SOR) solver is applied.

|           | Program    | Parameters                                 | Inst. (M) | Reads (M) | Writes (M) |

|-----------|------------|--------------------------------------------|-----------|-----------|------------|

|           | Cholesky   | tk15.O                                     | 584.4     | 201.8     | 27.7       |

|           | FFT        | 64K points                                 | 32.9      | 8.1       | 5.8        |

|           | $_{ m LU}$ | 512x512 matrix, $16x16$ blocks             | 340.6     | 97.6      | 47.8       |

| regular   | LU non-    | 512x512 matrix, $16x16$ blocks             | 340.9     | 97.5      | 47.8       |

|           | Ocean      | $258 \times 258$ , tolerance 10-7, steps 4 | 282.3     | 81.6      | 18.5       |

|           | Ocean-non  | 258 x 258, tolerance 10-7, steps 4         | 477.4     | 101.8     | 17.8       |

|           | Radix      | 1024  K keys, radix  = 1024                | 47.9      | 11.2      | 6.6        |

| particle  | Barnes     | 16K particles                              | 2569.0    | 861.0     | 575.1      |

|           | FMM        | 16K particles                              | 1035.7    | 232.8     | 38.7       |

| irregular | Radiosity  | room -ae 5000.0 -en 0.050 -bf 0.10         | 2878.5    | 574.8     | 305.8      |

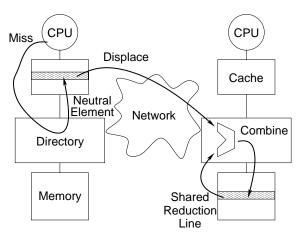

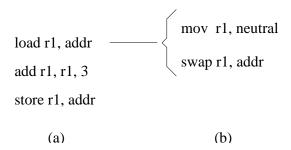

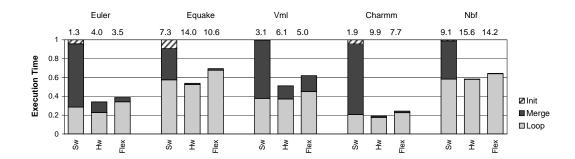

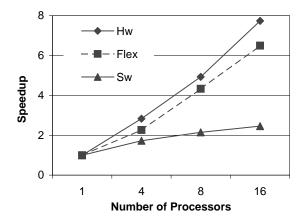

|           | Raytrace   | car                                        | 994.0     | 228.6     | 117.6      |