Departamento de Informática e Ingeniería de Sistemas Instituto de Investigación en Ingeniería de Aragón Grupo de Arquitectura de Computadores (gaZ)

# CONTRIBUTIONS TO HIGH-PERFORMANCE MEMORY HIERARCHIES: PROGRAM CHARACTERIZATION, RESOURCE CONTROL, TRANSACTIONAL SYNCHRONIZATION, AND HARDWARE PREFETCHING

by

Agustín Navarro Torres

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy in the Universidad de Zaragoza

January 31, 2023

Supervisors Pablo Enrique Ibáñez Marín Jesús Alastruey Benedé

#### **Abstract**

The increase in the number of cores and threads per processor over the last 15 years has allowed continuous improvements in system performance to be maintained. This design trend has involved major changes in the memory hierarchy. This dissertation explores new approaches to improve the performance of a multicore processor's memory hierarchy. Specifically, we analyze the utilization of its shared resources and propose mechanisms to improve the management of these resources from different levels ranging from the hardware to the application.

First, memory hierarchy performance has been evaluated for two SPEC CPU suites, CPU2006 and CPU2017, on an Intel Xeon Skylake-SP. This characterization has provided us with interesting findings, such as, for example, the unequal use of cache space by different applications or the effectiveness of hardware prefetching to reduce cache misses and improve system performance. This information served as a basis for defining new concrete objectives.

Next, we characterize the relationship between cache occupation, hardware prefetch and memory bandwidth consumption to understand their interactions. From this characterization work, we have proposed Balancer, a mechanism that dynamically imposes limits on LLC space usage and memory traffic to specific applications. These constraints improve performance and/or fairness in the execution of multiprogrammed workloads compared to an uncontrolled system. Balancer requires no hardware or operating system modifications.

As observed in the previous characterizations, data prefetching is a crucial technique as it allows hiding long-latency memory accesses and improving performance on modern high-performance processors. However, these prefetchers load a large number of useless blocks. This results in an unnecessary increase in the consumption of shared and scarce resources such as cache space and memory bandwidth. We propose Berti, a lightweight, highly accurate, energy-efficient, and high-performing local delta prefetcher that outperforms state-of-the-art prefetchers. Berti is an L1D prefetcher that orchestrates its requests across the entire cache hierarchy. Thanks to its high accuracy, Berti neither pollutes the caches nor wastes memory hierarchy bandwidth.

Synchronization between threads of the same application is another context where there can also be a high demand for shared resources in the memory hierarchy as the number of cores per processor increases. This dissertation presents a comprehensive study on the scalability of the different strategies that have been used for implementing synchronization solutions. The main conclusions that can be drawn are 1) hardware transactional memory scales better than fine-grained and non-blocking locks as the number of threads increases; 2) hardware transactional memory adoption is easy in real-world scientific applications and obtains performance comparable to that of a highly optimized locking scheme; and 3) enabling simultaneous multithreading for applications that access large memory blocks within their critical sections significantly affects the hardware transactional memory commit rate. In this context, we propose a novel cache replacement algorithm that aims to mitigate the negative effects of simultaneous multithreading on the transactional capacity abort rate.

#### Resumen

El aumento del número de núcleos e hilos por procesador en los últimos 15 años ha permitido mantener mejoras continuas en el rendimiento de los sistemas. Esta tendencia de diseño ha implicado importantes cambios en la jerarquía de memoria. Esta tesis explora nuevos enfoques para mejorar el rendimiento de la jerarquía de memoria de un procesador multinúcleo. En concreto, analizamos la utilización de sus recursos compartidos y proponemos mecanismos para mejorar la gestión de estos recursos en distintos niveles que van desde el hardware hasta la aplicación.

En primer lugar, se ha evaluado el rendimiento de la jerarquía de memoria para dos suites de SPEC, CPU2006 y CPU2017, en un Intel Xeon Skylake-SP. Esta caracterización nos ha proporcionado hallazgos interesantes, como, por ejemplo, el uso desigual del espacio de cache por parte de distintas aplicaciones o la eficacia de la prebúsqueda hardware para reducir los fallos de cache y mejorar el rendimiento del sistema. Esta información sirvió de base para definir nuevos objetivos concretos.

A continuación, caracterizamos la relación entre la ocupación de la cache, la prebúsqueda hardware y el consumo de ancho de banda con memoria para comprender sus interacciones. A partir de este trabajo de caracterización, hemos propuesto Balancer, un mecanismo que impone dinámicamente límites en el uso del espacio de la LLC y el tráfico con memoria a aplicaciones específicas. Estas restricciones mejoran el rendimiento y/o la equidad en la ejecución de cargas de trabajo multiprogramadas en comparación con un sistema no controlado. Balancer no requiere modificaciones en el hardware ni en el sistema operativo.

Como se ha observado en las caracterizaciones anteriores, la prebúsqueda de datos es una técnica crucial, ya que permite ocultar los accesos a memoria de larga latencia y mejorar el rendimiento en los procesadores modernos de alto rendimiento. Sin embargo, estos prebuscadores cargan un gran número de bloques inútiles. Esto se traduce en un aumento innecesario del consumo de recursos compartidos y escasos, como el espacio de cache y el ancho de banda con memoria. Proponemos Berti, un prebuscador hardware ligero, muy preciso, eficiente energéticamente y de alto rendimiento basado en deltas locales

que supera a los prebuscadores que conforman el estado del arte actual. Berti es un prebuscador de L1D que organiza sus peticiones a lo largo de toda la jerarquía de caches. Gracias a su gran precisión, Berti no contamina las caches ni desperdicia ancho de banda de la jerarquía con memoria.

La sincronización entre hilos de una misma aplicación es otro contexto en el que también puede haber una gran demanda de recursos compartidos en la jerarquía de memoria a medida que aumenta el número de núcleos por procesador. Esta tesis presenta un estudio exhaustivo sobre la escalabilidad de las diferentes estrategias que se han utilizado para implementar soluciones de sincronización. Las principales conclusiones que se pueden extraer son: 1) la memoria transaccional hardware escala mejor que los fine-grain locks y algoritmos lock-free a medida que aumenta el número de hilos; 2) la adopción de la memoria transaccional hardware es fácil en aplicaciones científicas y obtiene un rendimiento comparable al de un esquema de fine-grain locks altamente optimizado; y 3) habilitar el multihilo simultáneo para aplicaciones que acceden a grandes bloques de memoria dentro de sus secciones críticas afecta significativamente a la tasa de retiro de la memoria transaccional hardware. En este contexto, proponemos un novedoso algoritmo de reemplazo de cache que pretende mitigar los efectos negativos del multithreading simultáneo sobre la tasa de abortos por capacidad.

#### Acknowledgments

I would like to thank my official supervisors, Pablo and Chus, and my "third" supervisor, Victor, for their help and patience during all these years, this thesis would not have seen the light without their dedication and support. To my parents and my sister for their support during all these years.

To the GazBees (Adrián, Angélica, Carlos and Alba) for being there all these years and to the rest of the GAZ for welcoming me.

To Maria from Huawei Reseach Center Zürich, as well as Alberto Ros, Sawan and the rest of the research group at the University of Murcia for opening their doors and made me feel like home.

To Biswa for helping me to *prefetch* my first MICRO and guiding me in using ChampSim.

To my friends, especially Bea and Alberto, for being there during all these years. To Elba for her company at conferences.

#### **Publications**

Part of this dissertation includes results already published or accepted for publication.

The list of publications in chronological order are:

- Agustín Navarro-Torres, Jesús Alastruey-Benedé, Pablo Ibáñez-Marín, Víctor Viñals-Yúfera. Memory Hierarchy Characterization of SPEC CPU2006 and SPEC CPU2017 on the Intel Xeon Skylake-SP. PLOS ONE 14(8): e0220135, 2019. https://doi.org/10.1371/journal.pone.0220135. JCR 2019: Q2

- 2. **Agustín Navarro-Torres**, Maria Carpen-Amarie, Jesús Alastruey-Benedé, Pablo Ibáñez-Marín. *Synchronization Strategies on Many-Core SMT Systems*. 33rd International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2021), October 26-29, 2021, Belo Horizonte, Brasil. CORE B

- 3. Agustín Navarro-Torres, J. Alastruey-Benedé, Pablo Ibáñez, and Víctor Viñals-Yúfera. Berti: an Accurate Local-Delta Data Prefetcher. 55th ACM/IEEE International Symposium on Microarchitecture (MICRO 2022), October 1-5, 2022, Chicago, Illinois, USA. GGS 2(A). HiPEAC Paper Award given by the HiPEAC steering committee. HiPEAC is the High-Performance and Embedded Architecture and Compilation Network of Excellence (EC Contract No. 287759, http://www.hipeac.net)

- 4. **Agustín Navarro-Torres**, J. Alastruey-Benedé, Pablo Ibáñez, and Víctor Viñals-Yúfera. *BALANCER: Bandwidth Allocation and Cache Partitioning for Multicore Processors*. Accepted for publication at The Journal of Supercomputing, 2023. JCR 2021: Q2.

#### **Abbreviations**

CMP Chip Multicore Processor SLLC Shared Last Level Cache

HTM Hardware Transactional Memory

STM Software Transactional Memory

SMT Simultaneous MultiThreading

SKL-SP Skylake Scalable Processor

CCD Compute Core Die CCX Core CompleX

Intel-RDTIntel Resources Director exTensionsIntel-CATIntel Cache Allocation TechnologyIntel-MBAIntel Memory Bandwidth AllocationTSXTransactional Synchronization Extensions

HLE Intel Hardware Lock Elision

RTM Intel Restricted Transactional Memory

AMD QoSE AMD64 Technology Platform Quality of Service Extensions

L2A L2 Data Cache Spatial Prefetcher L2P L2 Data Cache Streamer Prefetcher

CPU2006

SPEC CPU 2006

CPU2017

SPEC CPU 2017

FP

Floating Point

CPI Cycles Per Instruction

APKI Accesses Per Kilo Instruction HPKI Hits Per Kilo Instruction

DMPKI Demand Misses Per Kilo Instruction

MPKI Misses Per Kilo Instruction

rBW read main memory BandWidth

CCO Control of SLLC Occupancy

CMT Control of Memory Traffic

CAS Compare-and-Swap

MOPS Million Operations Per Second

IP Instruction Pointer

## Contents

| Li | st of | Figur         | es                                                      | 13 |

|----|-------|---------------|---------------------------------------------------------|----|

| Li | st of | Table         | $\mathbf{s}$                                            | 17 |

| 1  | Intr  | oduct         | ion                                                     | 19 |

|    | 1.1   | Ratio         | nale                                                    | 19 |

|    | 1.2   | Contr         | ibutions                                                | 20 |

|    |       | 1.2.1         | Characterization of Application Use of Shared Resources | 21 |

|    |       | 1.2.2         | Shared Resource Control Mechanisms in the Memory        |    |

|    |       |               | Hierarchy                                               | 21 |

|    |       | 1.2.3         | Resource-efficient Hardware Data Prefetcher             | 22 |

|    |       | 1.2.4         | Study of the Use of Shared Resources by Different Syn-  |    |

|    |       |               | chronization Mechanisms                                 | 23 |

|    | 1.3   |               | tation Overview                                         | 24 |

|    | 1.4   | Thesis        | s project framework                                     | 25 |

| 2  | Mer   | norv I        | Hierarchy Characterization of SPEC CPU2006 and          |    |

| _  |       | U <b>2017</b> |                                                         | 27 |

|    | 2.1   | Introd        | luction                                                 | 27 |

|    | 2.2   |               | of the Art                                              | 28 |

|    |       | 2.2.1         | Benchmark Characterization Methodologies                | 29 |

|    |       | 2.2.2         | Selection of Benchmarks and Simulation Intervals        | 30 |

|    | 2.3   | Exper         | imental Framework                                       | 31 |

|    |       | 2.3.1         | Intel SKL-SP Memory Hierarchy                           | 31 |

|    |       | 2.3.2         | Runtime Environment                                     | 32 |

|    |       | 2.3.3         | Control Tools                                           | 32 |

|    |       | 2.3.4         | Monitoring and Instrumentation Tools                    | 32 |

|    |       | 2.3.5         | Workloads                                               | 34 |

|    |       | 2.3.6         | Metrics                                                 | 34 |

|    | 2.4   | Evalua        | ation                                                   | 37 |

|    |       | 2.4.1         | Identification of Memory Intensive Benchmarks           | 37 |

|    |       | 2.4.2         | Sensitivity to LLC Size and Hardware Prefetching        | 39 |

|    |       | 2.4.3         | Performance of the Hardware Prefetchers                 | 46 |

|    |       | 2.4.4         | Temporal Evolution of the Benchmarks                    | 46 |

|   | 2.5            | Concl  | uding Remarks                                        | 52         |

|---|----------------|--------|------------------------------------------------------|------------|

| 3 |                |        | · · · · · · · · · · · · · · · · · · ·                | 55         |

|   | 3.1            |        |                                                      | 55         |

|   | 3.2            |        | O.√                                                  | 57         |

|   |                | 3.2.1  | 0                                                    | 57         |

|   |                | 3.2.2  |                                                      | 58         |

|   |                | 3.2.3  | O                                                    | 58         |

|   |                | 3.2.4  |                                                      | 60         |

|   |                | 3.2.5  |                                                      | 61         |

|   | 3.3            | Chara  |                                                      | 62         |

|   |                | 3.3.1  | 1 0                                                  | 62         |

|   |                | 3.3.2  | Performance vs. Memory Bandwidth                     | 64         |

|   |                | 3.3.3  | Multiprogrammed Workload                             | 65         |

|   | 3.4            | Balan  | cer                                                  | 68         |

|   |                | 3.4.1  | Control of SLLC Occupancy (CCO)                      | 68         |

|   |                | 3.4.2  |                                                      | 69         |

|   |                | 3.4.3  | Balancer: Simultaneous Control of SLLC Occupancy and |            |

|   |                |        | Memory Traffic (CCO+CMT)                             | 71         |

|   | 3.5            | Evalua |                                                      | 71         |

|   |                | 3.5.1  |                                                      | 71         |

|   |                | 3.5.2  |                                                      | 71         |

|   |                | 3.5.3  |                                                      | 73         |

|   |                | 3.5.4  |                                                      | 74         |

|   |                | 3.5.5  |                                                      | 75         |

|   | 3.6            | Relate | v                                                    | 76         |

|   | 3.7            |        |                                                      | 77         |

|   |                |        | Ŭ                                                    |            |

| 4 | $\mathbf{Ber}$ |        |                                                      | <b>7</b> 9 |

|   | 4.1            | Introd |                                                      | 79         |

|   |                | 4.1.1  | Our Approach                                         | 80         |

|   |                | 4.1.2  |                                                      | 81         |

|   | 4.2            | Recen  | t Works and Motivation                               | 83         |

|   |                | 4.2.1  | Recent Advances in Data Prefetching                  | 83         |

|   |                | 4.2.2  | Motivation: Why a New Delta Prefetcher?              | 84         |

|   | 4.3            | Berti: | A Local-Delta Prefetcher                             | 86         |

|   |                | 4.3.1  | Training the Prefetcher                              | 87         |

|   |                | 4.3.2  | Prediction: Issuing Prefetch Requests                | 89         |

|   |                | 4.3.3  |                                                      | 89         |

|   | 4.4            |        | <del>-</del>                                         | 93         |

|   |                | 4.4.1  |                                                      | 93         |

|   |                | 4.4.2  |                                                      | 94         |

|   |                | 4.4.3  |                                                      | 94         |

|   |                | 4.4.4  |                                                      | 94         |

|   |                | 4.4.5  | · · · · · · · · · · · · · · · · · · ·                | 95         |

|   | 15             |        | -                                                    | o =        |

| 4.5.2Performance of Berti as an L1D Prefetcher94.5.3Multi-level Prefetching Performance104.5.4Memory Hierarchy Traffic and Energy104.5.5Effect of Constrained DRAM Bandwidth104.5.6CloudSuite Performance10 | )1<br>)3<br>)4<br>)4<br>)5<br>)6 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4.5.4 Memory Hierarchy Traffic and Energy                                                                                                                                                                   | )1<br>)3<br>)4<br>)4<br>)5       |

| 4.5.5 Effect of Constrained DRAM Bandwidth 10                                                                                                                                                               | )3<br>)4<br>)4<br>)5<br>)6       |

|                                                                                                                                                                                                             | )4<br>)4<br>)5<br>)6             |

| 4.5.6 CloudSuite Performance                                                                                                                                                                                | )4<br>)5<br>)6                   |

|                                                                                                                                                                                                             | )5<br>)6                         |

| 4.5.7 Interaction With a Temporal Prefetcher 10                                                                                                                                                             | )6                               |

| 4.5.8 Multi-core Performance                                                                                                                                                                                |                                  |

| 4.5.9 Sensitivity to Design Choices                                                                                                                                                                         | 8(                               |

| 4.6 Related Work                                                                                                                                                                                            | -                                |

| 4.6.1 Temporal Prefetchers                                                                                                                                                                                  | )8                               |

| 4.6.2 Spatial Prefetchers                                                                                                                                                                                   | -                                |

| 4.6.3 Machine Learning for Hardware Prefetching 10                                                                                                                                                          | )9                               |

| 4.6.4 Prefetch Filters and Throttling Mechanisms 10                                                                                                                                                         | )9                               |

| 4.7 Concluding Remarks                                                                                                                                                                                      | )9                               |

| 5 Synchronization Strategies on Many-Core Systems 11                                                                                                                                                        | 11                               |

| 5.1 Introduction                                                                                                                                                                                            | 1                                |

| 5.2 Background on Synchronization Strategies                                                                                                                                                                | .3                               |

| 5.2.1 Classical Strategies                                                                                                                                                                                  | .3                               |

| 5.2.2 Transactional Memory                                                                                                                                                                                  | 3                                |

| 5.3 Scalability Analysis of Synchronization Mechanisms 11                                                                                                                                                   | 5                                |

| 5.3.1 Experimental Setup and Methodology 11                                                                                                                                                                 | 15                               |

| 5.3.2 Concurrent Hash-Table                                                                                                                                                                                 | 7                                |

| 5.3.3 Concurrent Binary Search Tree                                                                                                                                                                         | 22                               |

| 5.4 Case Study: HTM Ease-of-Use                                                                                                                                                                             | 24                               |

| 5.5 SMT Impact on HTM Capacity Aborts                                                                                                                                                                       | 26                               |

| 5.5.1 Evaluation                                                                                                                                                                                            | 26                               |

| 5.5.2 Transaction-Aware Replacement Algorithm 12                                                                                                                                                            | 27                               |

| 5.5.3 TA-LRU Prototype                                                                                                                                                                                      | 28                               |

| 5.6 Related Work                                                                                                                                                                                            | 29                               |

| 5.7 Concluding Remarks                                                                                                                                                                                      | 30                               |

| 6 Conclusions and Future Work 13                                                                                                                                                                            | 31                               |

| 6.1 Conclusions                                                                                                                                                                                             | 31                               |

| 6.2 Future work                                                                                                                                                                                             | 33                               |

| 6.3 Conclusiones y Trabajo Futuro                                                                                                                                                                           |                                  |

| 6.3.1 Conclusiones                                                                                                                                                                                          |                                  |

| 6.4 Future Work                                                                                                                                                                                             |                                  |

| Bibliography 13                                                                                                                                                                                             | 39                               |

## List of Figures

| 1.1 | 50 years of microprocessor trend data [142]                                                                                                                                                                                                                                                                                                                              | 20 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

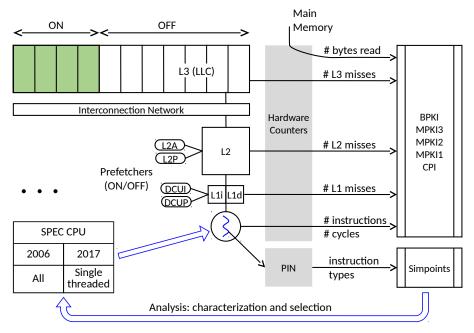

| 2.1 | Outline of the methodology                                                                                                                                                                                                                                                                                                                                               | 33 |

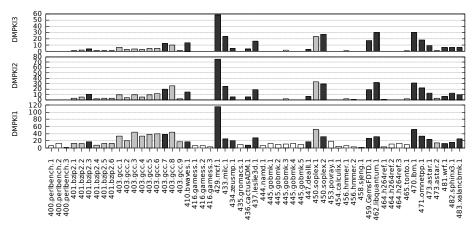

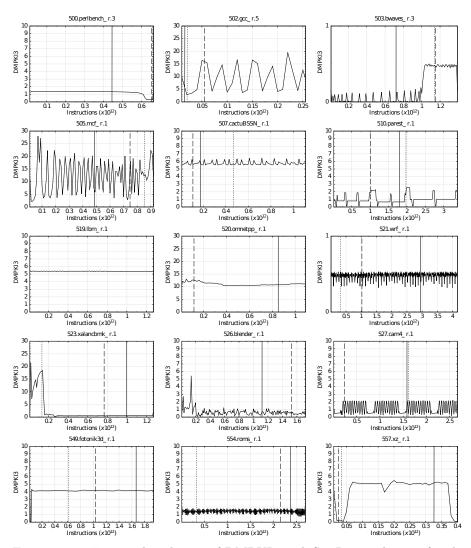

| 2.2 | DMPKI1, DMPKI2 and DMPKI3 for all SPEC CPU2006 benchmarks, sorted by benchmark number.                                                                                                                                                                                                                                                                                   | 37 |

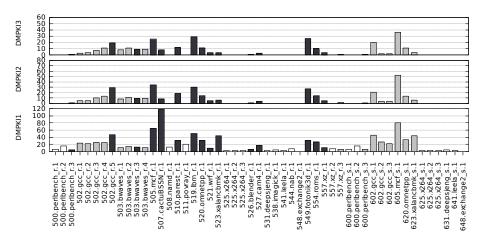

| 2.3 | DMPKI1, DMPKI2 and DMPKI3 for all SPEC CPU2017 single-threaded benchmarks, sorted by benchmark number                                                                                                                                                                                                                                                                    | 38 |

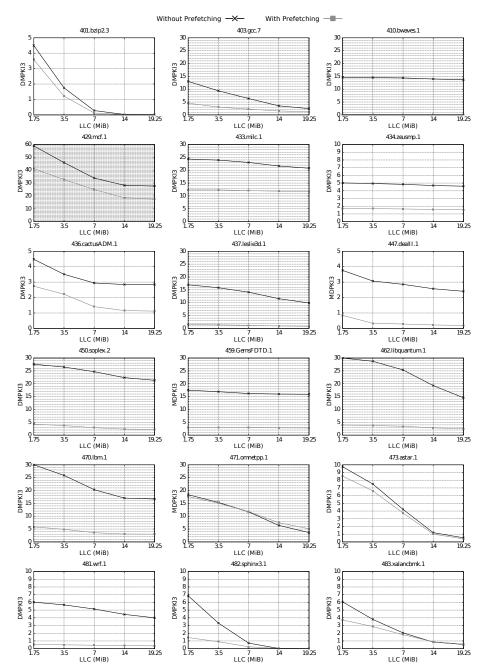

| 2.4 | DMPKI3 vs. SLLC size for the selected CPU2006 benchmarks, with and without prefetching                                                                                                                                                                                                                                                                                   | 40 |

| 2.5 | DMPKI3 vs. SLLC size for the selected CPU2017 benchmarks, with and without prefetching                                                                                                                                                                                                                                                                                   | 41 |

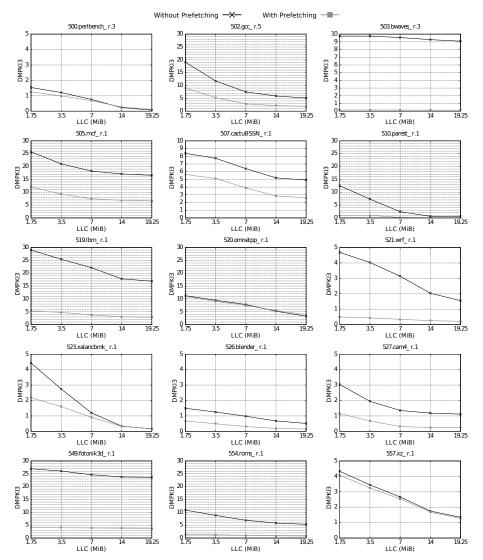

| 2.6 | Speed-ups enabled either by hardware prefetching, with the minimum cache size (X axis) or maximum SLLC size, without prefetching (Y axis) over a baseline configuration without prefetching and minimum SLLC size for the selected CPU2006 and CPU2017 benchmarks. Integer and floating point benchmarks are represented by gray circles and black squares, respectively | 42 |

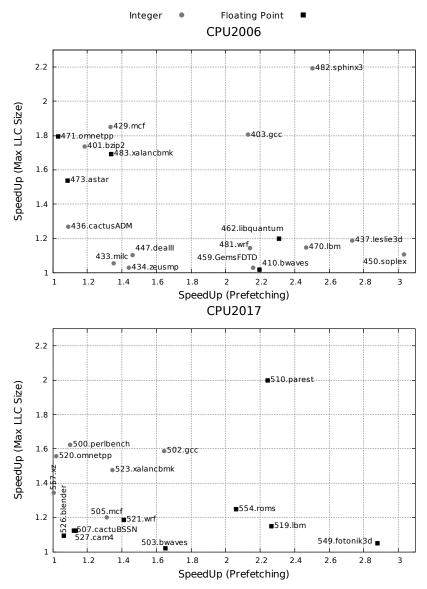

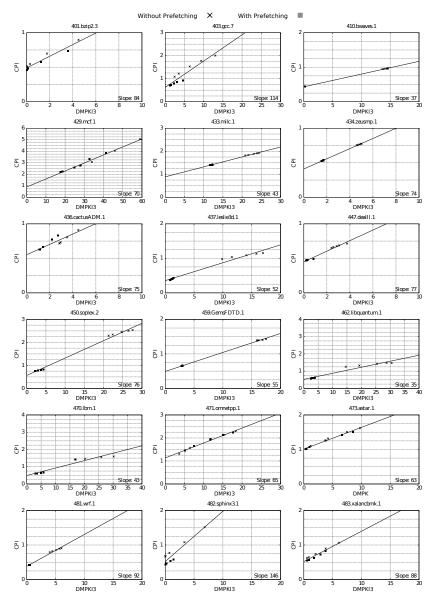

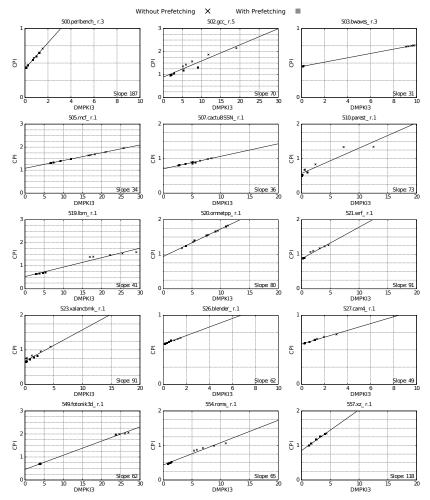

| 2.7 | CPI vs. DMPKI3 for the selected CPU2006 benchmarks, varying SLLC size and with prefetching (square marks) and without prefetching (x marks). Slope units are cycles/miss. Slopes are comparable in all graphs because the ratio between X and Y scales is constant (10:1)                                                                                                | 44 |

| 2.8 | CPI vs. DMPKI3 for the selected CPU2017 benchmarks, varying SLLC size and with prefetching (square marks) and without prefetching (x marks). Slope units are cycles/miss. Slopes are comparable in all graphs because the ratio between X and Y scales is constant (10:1)                                                                                                | 45 |

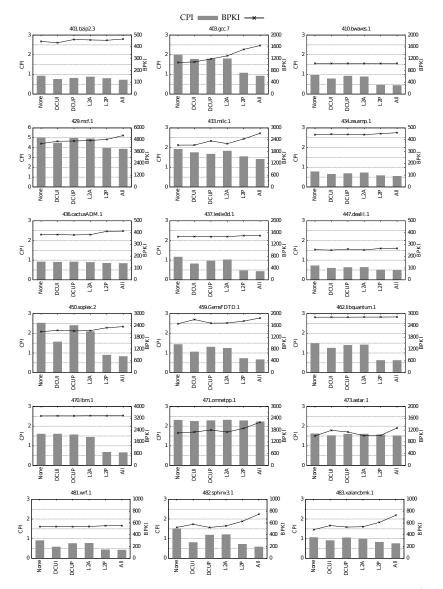

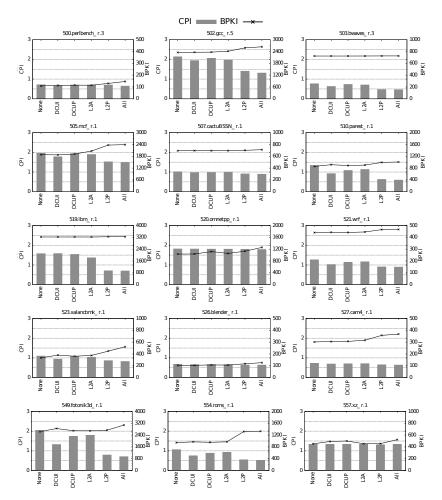

| 2.9 | Impact of the different hardware prefetchers on performance (CPI, bars) and bandwidth consumption (BPKI, line) for the selected CPU2006 benchmarks                                                                                                                                                                                                                       | 47 |

| 2.10       | Impact of the different hardware prefetchers on performance (CPI, bars) and bandwidth consumption (BPKI, line) for the selected CPU2017 benchmarks                                                                                                                      | 48                              |

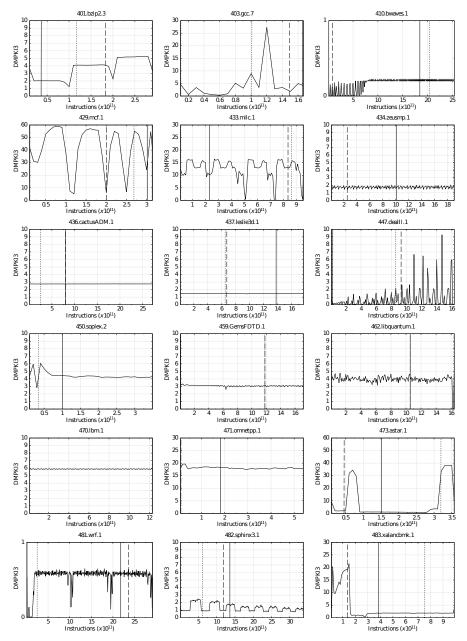

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2.11       | Temporal evolution of DMPKI3 and $SimPoint$ selection for the selected CPU2006 benchmarks, with minimum SLLC size and hard-                                                                                                                                             |                                 |

| 2.12       | ware prefetching                                                                                                                                                                                                                                                        | <ul><li>49</li><li>50</li></ul> |

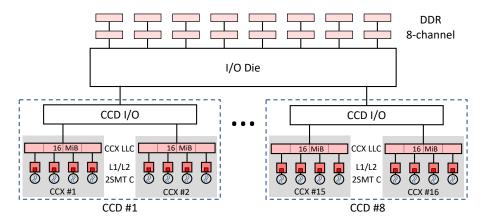

| 3.1        | AMD Rome 7702P clustered memory hierarchy. The multichip module has nine dies: eight CCD dies and one I/O die. In total there are 64 2-SMT cores (2SMT C) organized in 8 CCDs, each one with 2 CCX. Each CCX has a 16 MiB LLC shared by four cores [58].                | 58                              |

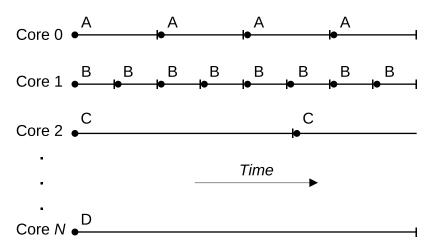

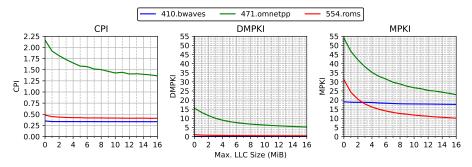

| 3.2<br>3.3 | Example of aplications completions in a mix execution CPI, DMPKI, and MPKI for increasing LLC allocation limits ( $1/16~{ m MiB}$                                                                                                                                       | 61                              |

| 3.4        | steps)                                                                                                                                                                                                                                                                  | 62                              |

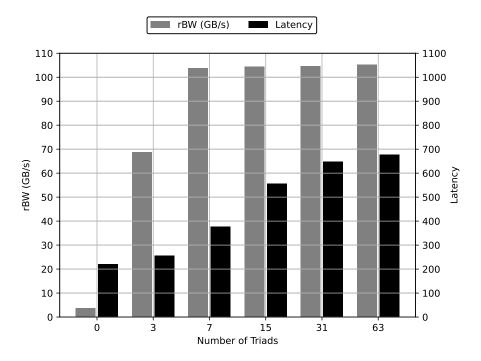

|            | Y-axis) vs. number of Triads (X-axis)                                                                                                                                                                                                                                   | 65                              |

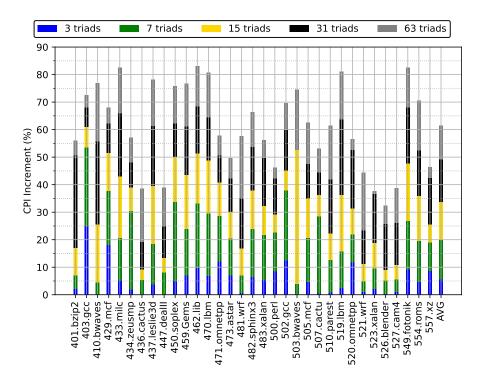

| 3.5        | CPI increase when running with multiple Triads                                                                                                                                                                                                                          | 66                              |

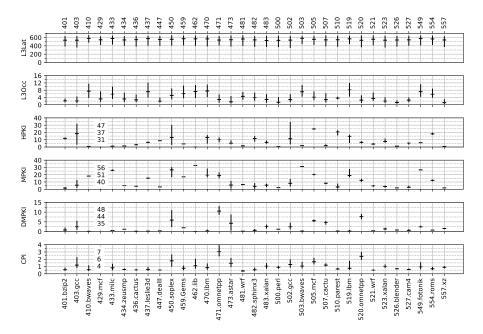

| 3.6        | CPI, DMPKI, MPKI, HPKI, L3Occ, and L3Lat. For each metric and application, the mean value and a vertical bar linking the minimum                                                                                                                                        | 07                              |

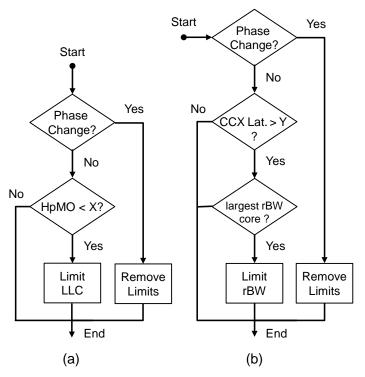

| 3.7        | and maximum values are shown                                                                                                                                                                                                                                            | 67<br>70                        |

| 3.8        | Speedup and unfairness for Balancer with different thresholds. Different colors and shapes represent results for different HpMO and                                                                                                                                     | 10                              |

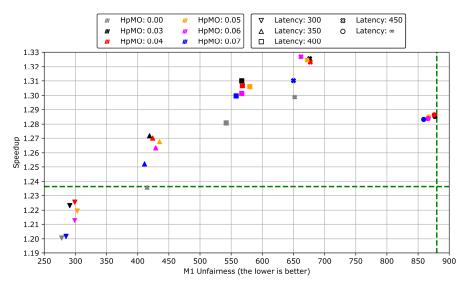

|            | latency thresholds, respectively. Green dashed lines correspond to an Uncontrolled system                                                                                                                                                                               | 72                              |

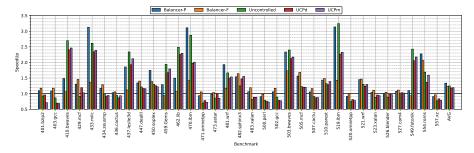

| 3.9        | Speedup of the selected SPEC CPU2006 and CPU2017 applications for all control mechanisms relative to Static                                                                                                                                                             | 73                              |

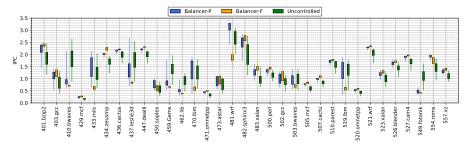

| 3.10       | IPC variability: 75th and 25th percentiles and maximum and minimum values                                                                                                                                                                                               | 75                              |

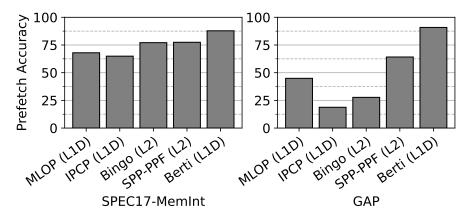

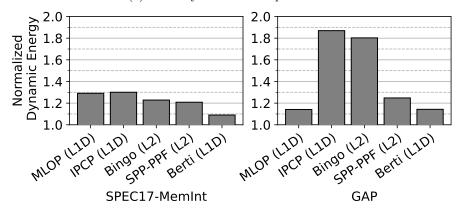

| 4.1        | Prefetch accuracy and dynamic energy consumption of the memory hierarchy for state-of-the-art prefetchers (IPCP [122], MLOP [145], SPP-PPF [13], and Bingo [9]) averaged across single-threaded traces from memory-intensive SPEC CPU2017 [119] and GAP [10] workloads. | Q1                              |

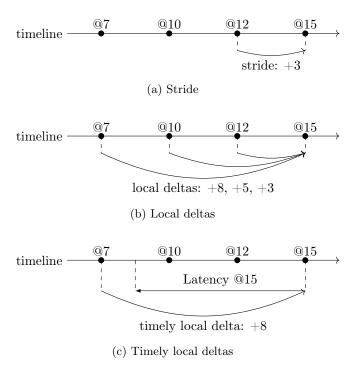

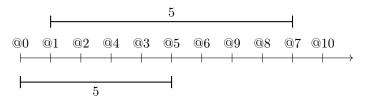

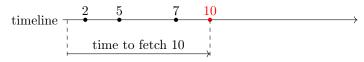

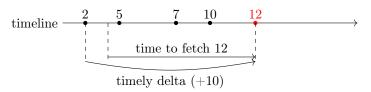

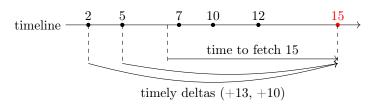

| 4.2        | Strides, local deltas and timely local deltas. The values on the timelines (7, 10, 12) represent the addresses referenced by the                                                                                                                                        | 01                              |

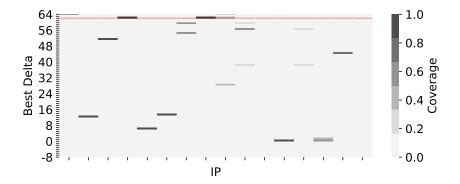

| 4.3        | same instruction                                                                                                                                                                                                                                                        | 82                              |

|            | in grayscale. BOP selects $+62$ as the best delta (red line), which is not always accurate and provides a coverage of only $2\%$                                                                                                                                        | 85                              |

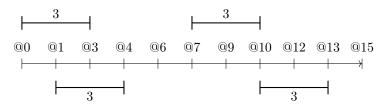

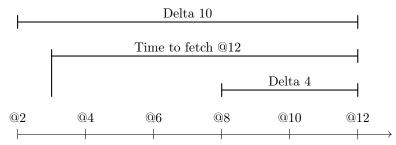

| 4.4        | +1, +2, memory miss pattern. Prefetching with delta 3 get 100% coverage                                                                                                                                                                                                 | 85                              |

| 4.5  | Memory reordering due to out-of-order processors. Prefetching with delta 5 get 100% coverage                                                                                                                         | 86  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.6  | +2 Memory miss pattern, with multiple possible deltas but only                                                                                                                                                       |     |

| 4 7  | delta +10 can hide the latency of @12 miss                                                                                                                                                                           | 86  |

| 4.7  | Access address 10: no timely delta found                                                                                                                                                                             | 88  |

| 4.8  | Access address 12: one timely delta found                                                                                                                                                                            | 88  |

| 4.9  | Access address 15: two timely deltas found                                                                                                                                                                           | 88  |

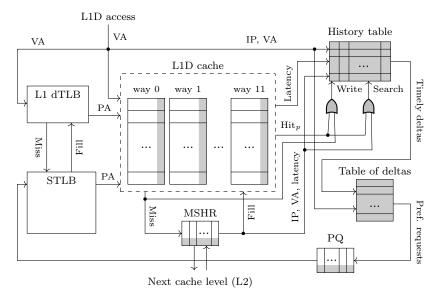

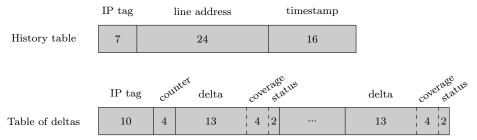

|      | Berti design overview. Hardware extensions are shown in gray. $\ .$ .                                                                                                                                                | 90  |

|      | History table and Table of deltas entry format                                                                                                                                                                       | 90  |

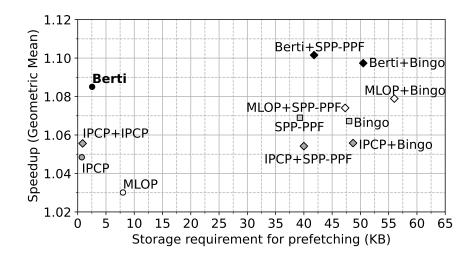

| 4.12 | Speedup vs. storage requirements. Speedup is normalized to L1D IP-stride and averaged across memory-intensive SPEC CPU2017 and GAP traces. $X+Y$ denotes prefetcher $X$ at L1D and prefetcher                        | 0.0 |

|      | Y at L2                                                                                                                                                                                                              | 96  |

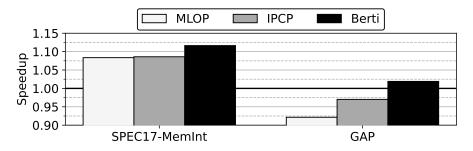

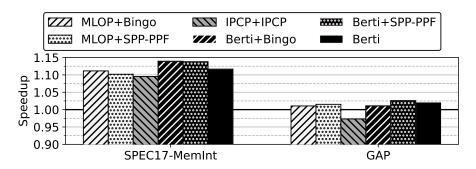

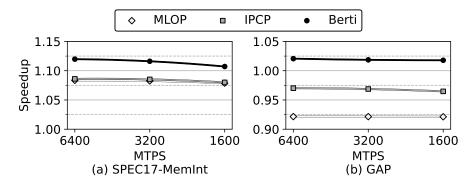

| 4.13 | Speedup of L1D prefetchers compared to a system with L1D IP-stride for memory-intensive SPEC CPU2017 and GAP traces                                                                                                  | 97  |

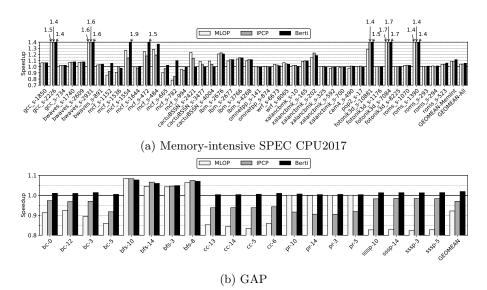

| 4.14 | Speedup with Berti as an L1D prefetcher for (a) 44 SPEC CPU2017 and (b) 20 GAP memory-intensive traces normalized to L1D IP-stride. Geomean-all corresponds to the geometric mean of all the 95 SPEC CPU2017 traces. | 97  |

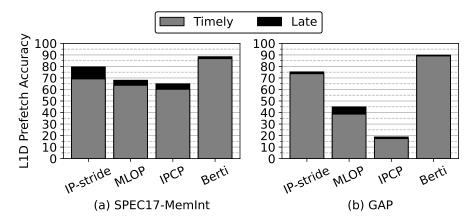

| 1 15 | Prefetch accuracy at the L1D. Percentages of useful requests are                                                                                                                                                     | 91  |

| 4.13 | broken down into timely (gray) and late (black) prefetch requests.                                                                                                                                                   | 99  |

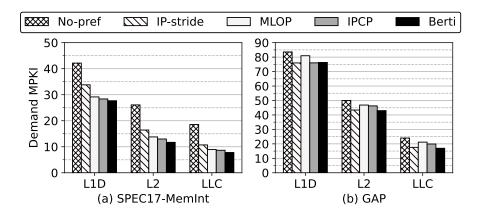

| 4.16 | Prefetch coverage in terms of average L1D, L2, and LLC demand                                                                                                                                                        |     |

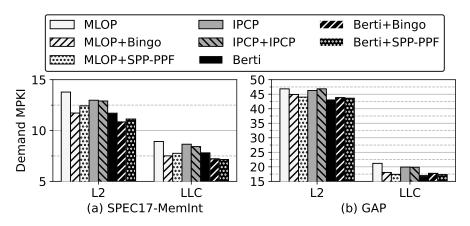

|      | MPKIs for all L1D prefetchers                                                                                                                                                                                        | 99  |

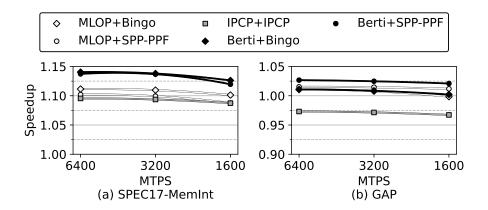

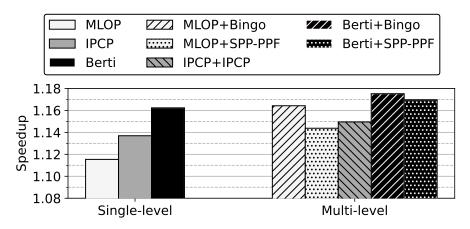

|      | Spedup with multi-level prefetching normalized to L1D IP-stride                                                                                                                                                      | 100 |

| 4.18 | Prefetch coverage in terms of average L2 and LLC demand MPKIs with multi-level prefetching                                                                                                                           | 101 |

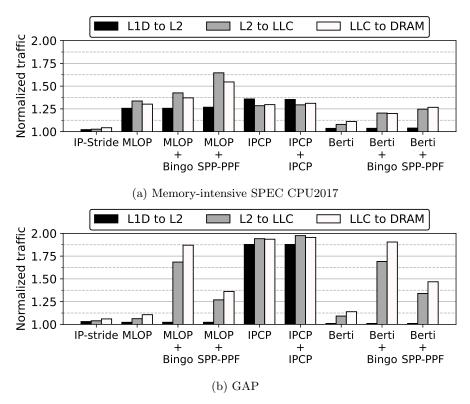

| 4.19 | L2, LLC and DRAM demand and prefetch traffic normalized to                                                                                                                                                           |     |

|      | no-prefetching                                                                                                                                                                                                       | 102 |

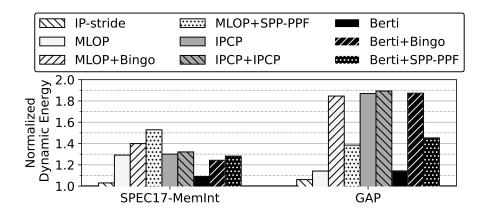

| 4.20 | Dynamic energy consumption in the memory hierarchy normalized                                                                                                                                                        |     |

|      | to no-prefetching.                                                                                                                                                                                                   | 103 |

| 4.21 | Performance of L1D prefetchers in constrained DRAM bandwidth, in MTPS                                                                                                                                                | 103 |

| 4.22 | Performance of multi-level prefetching in constrained DRAM bandwidth, in MTPS                                                                                                                                        | 104 |

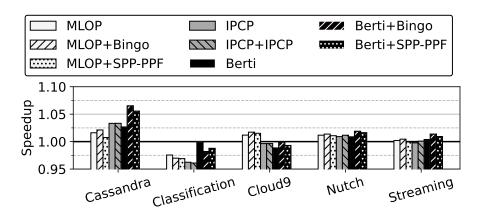

| 4 23 | Speedup for CloudSuite                                                                                                                                                                                               | 105 |

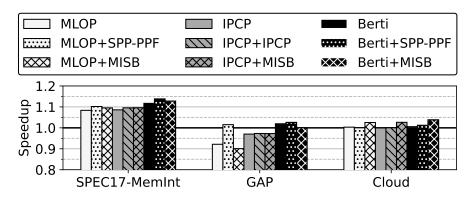

|      | Speedup with and without MISB                                                                                                                                                                                        |     |

|      |                                                                                                                                                                                                                      | 109 |

|      | Summary of multi-core speedups relative to a system with L1D IP-stride prefetcher                                                                                                                                    | 106 |

| 4.26 | Normalized speedup with different L1D and L2 confidence water-<br>marks averaged across memory intensive SPEC CPU2017 and GAP<br>benchmarks. Speedup is rounded to two decimal places (1.085 is                      |     |

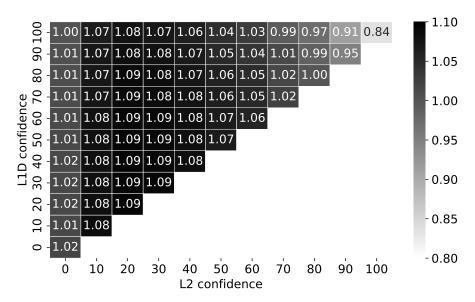

|      | rounded to 1.09)                                                                                                                                                                                                     | 107 |

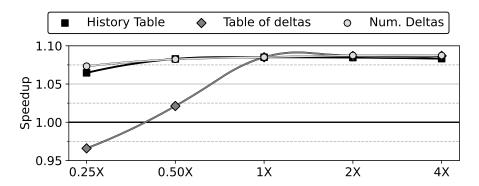

| 4.27 | Speedup vs. size of Berti tables and number of deltas. $0.25 \times$ to $4 \times$ correspond to one-fourth and four times, respectively                                                                             | 107 |

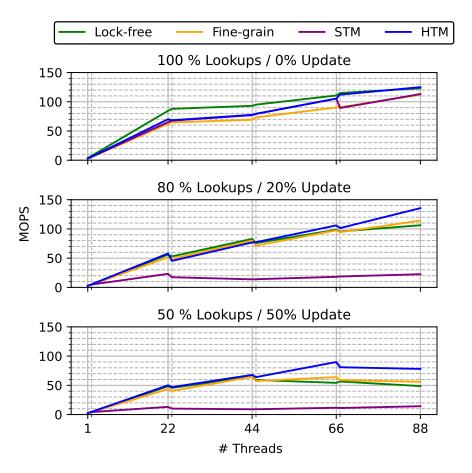

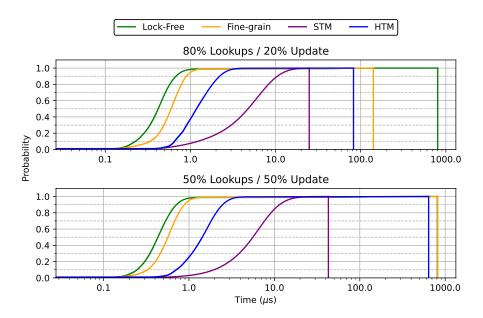

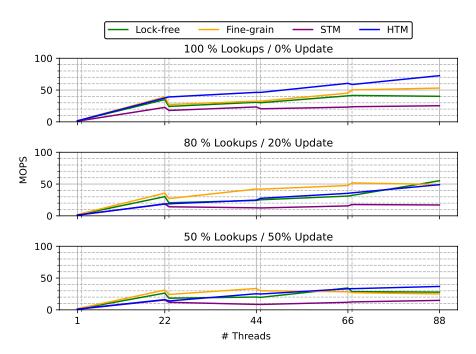

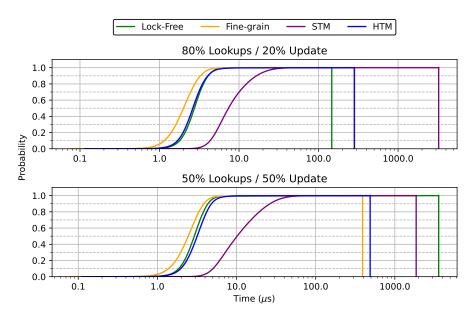

| 5.1  | Throughput of the different synchronization mechanisms on a con-      |     |

|------|-----------------------------------------------------------------------|-----|

|      | current hash-table                                                    | 118 |

| 5.2  | Update operation latency (88 threads) for the synchronization mech-   |     |

|      | anisms on a concurrent hash-table                                     | 119 |

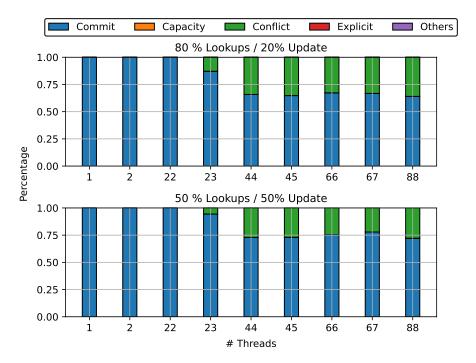

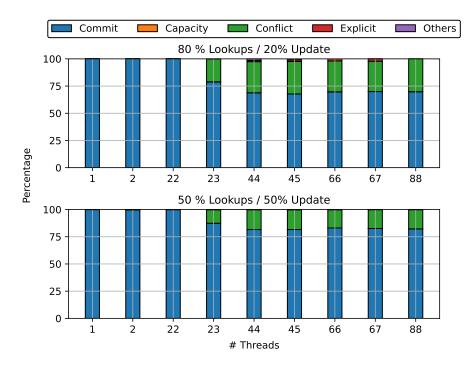

| 5.3  | HTM events of the different synchronization mechanisms on a con-      |     |

|      | current hash-table                                                    | 120 |

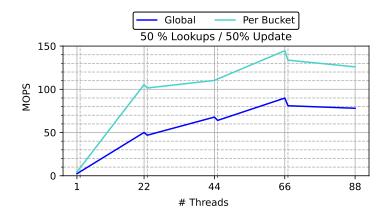

| 5.4  | Global fallback lock vs. per-bucket fallback lock                     | 121 |

| 5.5  | Throughput of the different synchronization mechanisms on a con-      |     |

|      | current BST                                                           | 122 |

| 5.6  | Operation latency (88 threads) of the different synchronization mech- |     |

|      | anisms on a concurrent BST                                            | 123 |

| 5.7  | HTM events of the different synchronization mechanisms on a con-      |     |

|      | current BST                                                           | 124 |

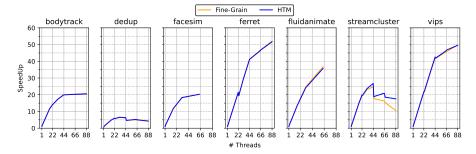

| 5.8  | HTM and fine-grained locking evaluation on PARSEC 3.0 benchmarks      | 125 |

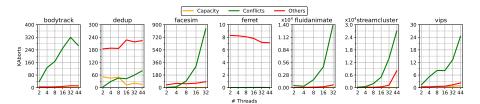

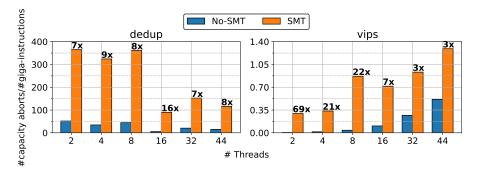

| 5.9  | Number of aborts per category in the Parsec 3.0 suite with SMT        | 126 |

| 5.10 | Capacity aborts in the PARSEC 3.0 with and without SMT and            |     |

|      | their ratio.                                                          | 127 |

## List of Tables

| 2.1        | SKL-SP system specifications                                                                                                                                                                                  | 32 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2        | Perf symbolic event types used                                                                                                                                                                                | 33 |

| 2.3        | Benchmarks tested, divided between integer (int column) and floating point (fp column). Filled cells in columns "2006" and "2017" mean the benchmark appears in the corresponding suite. The columns labeled  |    |

|            | "_r" and "_s" refer to the application versions producing SPECrate and SPECspeed metrics, respectively. Columns "Inst." and "#" show instruction count $(x10^{12})$ and input identifier, respectively.       | 35 |

| 2.4        | Used metrics                                                                                                                                                                                                  | 36 |

| 2.5        | Selected benchmarks and their performance metrics for minimum SLLC size and no prefetching                                                                                                                    | 38 |

| 3.1        | Summary of papers on resource management with real machine experimentation. LLC: last-level cache, which can be inclusive (I) or non-inclusive (NI). BW <sub>mem</sub> : memory bandwidth, IC: interconnect,  |    |

|            | MC: memory controller, Freq: core frequency, $BW_{disk}$ : disk bandwidth, #Cores: number of cores, $Pref_{hw}$ : hardware prefetcher, Net: Internet connection. The rows are arranged in chronological order |    |

|            | of the processor on which the mechanisms are applied                                                                                                                                                          | 56 |

| 3.2        | Main features of the selected server                                                                                                                                                                          | 59 |

| 3.3        | Metrics calculation from hardware counters [33, 32]                                                                                                                                                           | 59 |

| 3.4<br>3.5 | Used metrics                                                                                                                                                                                                  | 61 |

|            | turn have four cores each                                                                                                                                                                                     | 64 |

| 3.6        | Balancer-P and Balancer-F thresholds                                                                                                                                                                          | 73 |

| 3.7        | Average $M_1$ execution fairness                                                                                                                                                                              | 74 |

| 4.1        | Storage overhead of Berti                                                                                                                                                                                     | 92 |

| 4.2        | Simulation parameters of the baseline system                                                                                                                                                                  | 93 |

| 4.3        | Configurations of evaluated prefetchers                                                                                                                                                                       | 95 |

| 5.1 | Synchronization mechanisms with their benefits and drawbacks.     |     |

|-----|-------------------------------------------------------------------|-----|

|     | Non-portable stands for implementations that are dependent on the |     |

|     | architecture                                                      | 113 |

| 5.2 | Main characteristics of the workstation used in the evaluation    | 115 |

#### Introduction

#### 1.1 Rationale

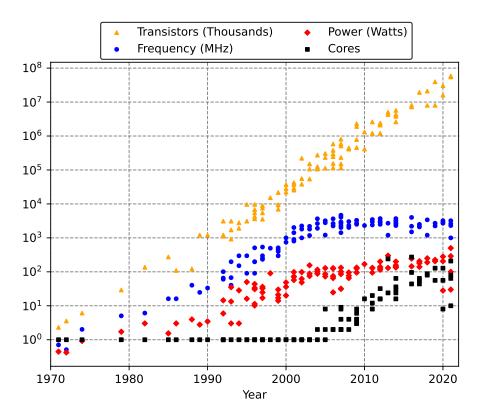

Over the past 50 years, the industry has enjoyed a continuous improvement in processor performance fueled by Moore's Law [106] and Dennard Scaling [31]. During the early years, this performance improvement was coupled with increasing processor frequency. However, when the power dissipation limit was reached, processor designers reduced the processors' frequency and resorted to multiple cores integration on the same chip to maintain performance growth over time. Figure 1.1 shows how the number of transistors (yellow triangle) has grown exponentially over the years (X-axis), while frequency (blue circles) and power (red diamonds) grew exponentially until 2005 when they stabilized, and the number of cores (black squares) began to increase.

Today chip multicore processors (CMPs) integrate several tens of cores, sometimes grouped in clusters. Each core, that can run one or more threads, has private resources (e.g.: the pipeline) and resources that are shared with other cores e.g.: a major part of the memory hierarchy. The memory hierarchy is a common solution for hiding part of the costly off-chip main memory access latency and avoiding the power consumption associated with its use. It is organized into levels, which increase in size, energy consumption and access latency. Usually, the first cache levels, those closest to the core, are private, while the last level of cache (LLC¹) is a shared resource. Likewise, the main memory access channels and the interconnection network that communicates cores, SLLC banks and memory channels are also shared resources.

This paradigm shift of processors, from a single fast core to many cores that share resources, has driven major changes in their design. Researchers and engineers do not have to achieve only the highest performance in an individual application, they must also improve the performance of the system as a whole and prevent applications from harming each other. Thus, the memory hierarchy, being the main shared resource, requires special attention in this context.

<sup>&</sup>lt;sup>1</sup>In this dissertation LLC and SLLC are used indistinctly.

Figure 1.1: 50 years of microprocessor trend data [142].

Memory hierarchy design constantly demands new architectural solutions as new trade-offs arise due to the significant increase in the number of cores on the chip, and the increased pressure on the hierarchy that comes with it.

#### 1.2 Contributions

The main objective of this thesis is to improve the efficiency in the use of shared resources in the memory hierarchy of a CMP. This goal can be achieved from different approaches, and by acting at different levels ranging from hardware to application. The contributions of the thesis attempt to improve our understanding of how applications use resources and to improve the way they use them. These contributions are four: 1) characterization of application use of shared resources such as LLC space and memory bandwidth, 2) shared resource control mechanisms in the memory hierarchy, 3) resource-efficient hardware data prefetcher, and 4) study of the use of shared resources by different synchronization mechanisms.

This section motivates the research lines, details the contributions, and

includes the results of the work.

### 1.2.1 Characterization of Application Use of Shared Resources

The experimental part of most research work in computer architecture consists of feeding a simulator or a real machine with programs representative of current or future software. There are a multitude of collections of such programs, each associated with a particular field of application [47, 45, 43, 120]. Understanding the behavior of each of these programs facilitates all experimentation tasks. It allows for example to select suitable samples to demonstrate the feasibility of an idea, or to analyze the results obtained when applying a technique taking into account the characteristics of the executed software. Consequently, application characterization is one of the first tasks of many research works and even the target of specific publications recurrently in the computer architecture community [87, 97, 15, 167].

At the beginning of the work of this thesis, several events occur that make the specific characterization work even more relevant: i) SPEC releases a new suite for general purpose computing, CPU2017, after eleven years since the previous version, CPU2006, ii) some vendors such as Intel significantly improve the tools for both information retrieval (hardware counters) and resource control (cache partitioning, prefetcher disconnection), and iii) Intel adopts for the first time the content management model of its LLC mostly in exclusion. Thus, the first objective raised in the thesis is the characterization of the new set of SPEC CPU2017 programs in the new Intel Xeon Skylake-SP memory hierarchy, and its comparison with the previous version, SPEC CPU2006. This characterization will provide information to define new concrete objectives in the rest of the work, and will facilitate all the experimentation work.

This characterization work is presented in **Chapter 2**. We evaluate the memory hierarchy behavior of the CPU2006 and CPU2017 SPEC single-thread benchmarks using different shared LLC sizes and prefetch configurations, on an Intel Xeon Skylake-SP. The evaluation is performed on a real machine, running the complete applications with all their reference inputs and using hardware counters to take the measures. This work has been published in *Plos One* (2019) [114]. All code and data are available at https://github.com/agusnt/Xeon-SP Memory Characterization SPEC-CPU-2K6-2K17/.

## 1.2.2 Shared Resource Control Mechanisms in the Memory Hierarchy

Advances in the scale of integration allow processors to have more and more cores. This trend means that shared resources, especially space in the LLC and memory bandwidth, are under increasing pressure. On the other hand, the execution of workloads composed of independent applications generates uneven resource demands. For example, some programs may require a lot of

cache space while others may consume a lot of memory bandwidth. Shared resource management is key to efficiently running such workloads on today's processors. In this regard, many proposals have been published with hardware mechanisms to share SLLC space between cores or the applications they run. Most of these proposals require hardware modifications and have been evaluated with a reduced number of cores.

Recently, several commercial processors have incorporated technologies that allow 1) monitoring the use of cache space and memory bandwidth by different cores, and 2) imposing limits on the consumption of these shared resources. For example, starting with the Skylake family, Intel processors have Intel Cache Allocation Technology (CAT) [78], AMD EPYC processors have AMD64 Technology Platform Quality of Service Extensions [69]. These functionalities allow the design of software mechanisms that implement shared resource management policies and require no hardware or operating system modifications for their operation.

Since hardware support for memory traffic management is more recent, works for controlling this resource are scarcer. Specifically, we are aware of only three proposals that address memory bandwidth sharing [129, 171, 130]. Moreover, almost all previous works focus on Intel's memory hierarchies, where the LLC is shared among all cores, so there are no proposals specifically designed for a clustered LLC organization, such as the one used by AMD in its current EPYC processors.

The goal of this thesis in this line of research is to design a mechanism that improves system performance and fairness by dynamically sharing LLC cache space and main memory bandwidth among running applications. To this end, **Chapter 3** presents a detailed characterization of the shared cache and memory bandwidth usage of an AMD Rome processor running multiprogrammed workloads. Then, it proposes Balancer, a set of mechanisms that control the use of these shared resources to improve system performance and fairness. Balancer requires no hardware or operating system modifications.

Balancer has been designed and evaluated in a clustered LLC such as that of the AMD Rome. Hence, it can make different decisions in each cluster in a decentralized manner, in response to their particular cache utilization and bandwidth consumption.

This work has been accepted for publication in the *Journal of Supercomputing (2023)*. All code and data are available at https://github.com/agusnt/BALANCER.

#### 1.2.3 Resource-efficient Hardware Data Prefetcher

Prefetching has proven to be a powerful mechanism for reducing the memory access penalty. Hardware prefetchers learn memory access patterns and use those patterns to load data into the cache hierarchy before the processor requests it. In this way, future processor accesses to memory will fetch the data from

nearby caches, with low latency. Prefetching techniques can be employed in the first-level private data cache (L1D), second-level cache (L2) or last-level shared cache (SLLC). Recently proposed prefetchers target both the L2 cache (Bingo [9]) and the L1 data cache (IPCP [122]). A common problem with all of them is their low accuracy. Often, the prefetchers make mistakes and load blocks that will never be used, causing pollution in the caches and extra consumption of memory bandwidth. This problem becomes more relevant as the number of cores increases as it causes an inefficient use of increasingly saturated shared resources. Ultimately, this inappropriate use results in a decrease in overall system performance and an increase in energy consumption.

Several mechanisms have been proposed to reduce the polution of prefetchers. For example, the Perceptron-based prefetch filter (PPF) is a filter that decides whether prefetched blocks are loaded in L2 or not [13]. Similar to PPF, there are proposals that control the aggressiveness of prefetchers by controlling their prefetch degree and prefetch distance, or decide whether to prefetch in L2 or in LLC [6, 42, 66, 125, 123, 124, 155]. These techniques achieve partially improved accuracy but entail additional storage.

The goal of this thesis with respect to prefetching is to propose a prefetch mechanism with very high accuracy, so that it minimizes the wasteful consumption of shared multicore processor resources such as shared cache space and bandwidth with main memory. Berti is proposed in **Chapter 4**, a new first-level data prefetcher that orchestrates prefetch requests to the memory hierarchy. Berti learns the best deltas per IP by a mechanism that calculates the coverage of each delta and selects those deltas that provide the highest coverage. Berti pushes further the limits of hardware prefetchers with minimal space storage requirements and high accuracy. This work has been published in the *IEEE/ACM International Symposium on Microarchitecture (2022)* [113]. All code and data are available at the artifact which received three badges at MICRO 2022: Artifacts Available, Artifacts Evaluated—Functional, Results Reproduced) https://github.com/agusnt/Berti-Artifact.

## 1.2.4 Study of the Use of Shared Resources by Different Synchronization Mechanisms

Previous contributions in this thesis are focused on improving the performance of systems running multiprogrammed workloads, i.e., a set of independent programs running simultaneously in the same computer. However, it is also important to improve the execution of parallel workloads, i.e., those composed of simultaneously running threads that collaborate to solve the same problem.

The stagnation in single-threaded performance improvement and its resulting shift toward multithreaded execution has changed how applications are developed. An application that wishes to take full advantage of the potential of a multicore processor should use as many threads as possible. This implies the use of several execution threads per core, or simultaneous multithreading (SMT), which increases the pressure on the private and shared resource of the memory hierarchy.

The use of a larger number of threads implies more concurrency, making synchronization mechanisms more important. The use of classical mechanisms such as fine-grain locks or lock-free mechanisms are complex, require in-depth knowledge of the program, and are error-prone. Transactional memory was developed to make this synchronization easier and improve its performance. In transactional memory, data conflicts are detected and handled by the memory hierarchy, making content management within the memory hierarchy even more important. With the appearance of the first hardware transactional memory implementations on commercial processors [98, 162, 83], numerous mechanisms have appeared that evaluate and compare their performance with classical synchronization mechanisms [18, 128, 143, 176].

However, to the best of our knowledge, there is no study that evaluates the scalability of all synchronization mechanisms together on many-core systems and that takes into account the impact of simultaneous multithreading (SMT). Furthermore, while SMT is recognized as a limiting factor for HTM performance [164], its impact is not clearly quantified and no solution has been proposed to mitigate it.

Chapter 5 focuses on evaluating the performance and operation latency of the most widely-used synchronization mechanisms: hardware transactional memory (HTM), software transactional memory (SMT), locks and lock-free. This chapter also study the impact of simultaneous multithreading (SMT) technology on HTM performance and propose a mechanism to reduce SMT-inducted aborts. This work has been published in the *IEEE International Symposium on Computer Architecture and High Performance Computing, SBAC-PAD (2021)* [115]. All code and data are available at https://github.com/agusnt/Synchronization-Strategies-on-Many-Core-SMT-Systems.

#### 1.3 Dissertation Overview

This dissertation is organized as follows. Chapter 2 characterizes SPEC CPU2006 and CPU2017 and its interaction with the Intel Xeon Skylake-SP memory hierarchy. In Chapter 3 presents Balancer a software mechanism that improve the system's performance and fairness. Then Chapter 4 presents Berti our proposal for a new L1D prefetcher. Chapter 5 shows an evaluation of different thread synchronization mechanisms in terms of performance an operation latency. Finally in Chapter 6 concludes the dissertation summarizing the work done and discusses about the new research lines.

A variety of methodologies and tools have been used during the completion of this doctoral thesis. In Chapter 2, a characterization work has been performed on a real system equipped with an Intel Skylake processor using hardware tools for resource monitoring and control (counters, model-specific registers, Intel CAT). Chapter 3 presents an experimentation and evaluation work on a real system, this time on a computer with an AMD EPYC processor using the hardware support of the platform (hardware counters, AMD QoSE). In Chapter 4 the proposal has been evaluated on a processor modeled with the ChampSim simulator. Chapter 5 includes experiments with real hardware (hardware transactional memory on Intel Cascade Lake) and simulation (Gem5). Therefore, the experimental environment and methodology are presented in each chapter since there is no common framework.

#### 1.4 Thesis project framework

This thesis has been developed at the Grupo de Arquitectura de Computadores de la Universidad de Zaragoza (gaZ), in the Departamento de Informática e Ingeniería de Sistemas (DIIS) and Instituto de Investigación en Ingeniería de Aragón (I3A).

The thesis and its research work has been funded by:

- Grant (BES-2017-079790) para la Formación de Personal Investigador (FPI) from the Spanish Ministry of Economy and Competitive.

- Project PID2019-105660RB-C21: Jerarquía de memoria, gestión de tareas y optimización de aplicaciones, from the Agencia Estatal de Investigación and TIN2016-76635-C2-1-R: Arquitectura y programación de computadores escalables de alto rendimiento y bajo consumo, from the Spanish Ministry of Economy and Competitive. Both projects are in collaboration with the University of Cantabria which led to a fruitful collaboration in this thesis.

- The Aragón Government has partially funded the work through the Research group recognition: T58\_20R research group from Aragón Government and European Social Fund, and (3) 2014-2020 "Construyendo Europa desde Aragón" from European Regional Development Fund.

I have developed two research internships. One of them at the Huawei research lab in Zürich (Switzerland) under the supervision of Maria Carpen-Amarie, funded by Huawei, and a second one at Grupo de Arquitectura de Computadores y Sistemas Paralelos (CAPS) of the Universidad de Murcia under the supervision of Alberto Ros Bardisa, thanks to a competitive grant for short stavs associated to the FPI.

## Memory Hierarchy Characterization of SPEC CPU2006 and CPU2017

SPEC CPU is one of the most common benchmark suites used in computer architecture research. In this chapter we present a detailed evaluation of the memory hierarchy performance for the CPU2006 and single-threaded CPU2017 benchmarks. The experiments were executed on an Intel Xeon Skylake-SP, which is the first Intel processor to implement a mostly non-inclusive SLLC. First, we present a classification of the benchmarks according to their memory pressure and analyze the performance impact of different SLLC sizes. Then, we test all the hardware prefetchers showing that they improve performance in most of the benchmarks. After a comprehensive experimentation, we can highlight the following conclusions: i) almost half of SPEC CPU benchmarks have very low miss ratios in the second and third level caches, even with small SLLC sizes and without hardware prefetching, ii) overall, the SPEC CPU2017 benchmarks demand even less memory hierarchy resources than the SPEC CPU2006 ones, iii) hardware prefetching is very effective in reducing SLLC misses for most benchmarks, even with the smallest SLLC size, iv) the SLLC utilization is uneven among applications, and v) from the memory hierarchy standpoint the methodologies commonly used to select benchmarks or simulation points do not quarantee representative workloads.

#### 2.1 Introduction

The majority of experimental research in computer architecture is based on feeding a simulator or a real machine with benchmarks that are representative of current or future software in a certain application field. The benchmark characterization is one of the first tasks to be carried out by the computer architecture community. Among its goals, we can highlight the classification of applications according to certain characteristics, the selection of samples for simulation, or the detection of non-optimal behaviors to detect flaws in the designs and improve it. These benchmarks suites can be developed by diverse corporations

(e.g. SPEC [120]), research groups (e.g. CloudSuite [47]), communities (e.g. TACLeBench [45]) and even certain companies (e.g. EEMBC [43]) propose benchmark suites composed of a number of applications focused on specific fields such as general purpose computing, cloud computing, real time or embedded processing, respectively. According to SPEC Corporation, SPEC CPU2017 contains a collection of next-generation and industry-standardized benchmarks aimed at stressing the processor, memory subsystem and compiler [119].

Implementing a new hardware concept in a real system is unfeasible in most cases, due to its high cost or the impossibility of its subsequent modification. An alternative is to use a simulator which models at the desired level of detail (e.g. cycle-level) the behavior of a complex system such as a multicore processor with a multi-level memory hierarchy and an interconnection network. However, the complete execution of a benchmark in these simulators may require months or even years. Thus, sampling techniques are used to identify small sections of a benchmark that approximate the behavior of the full application [165, 131].

Benchmarks with certain characteristics are selected to evaluate the performance of new proposals. For example, research on shared cache replacement algorithms frequently selects a mix of benchmarks with different degrees of pressure on the memory hierarchy: some of them show high cache utilization while others do the opposite [86, 2].

In this chapter, we characterize the interaction of the SPEC CPU2006 and CPU2017 suites with the Intel Xeon Skylake-SP memory hierarchy. The analysis of CPU2017 is of special interest since it is a recent suite [126]. Regarding the processors, it also brings relevance to this study because the Intel Xeon Skylake-SP family has been released in July 2017 and incorporates significant changes in the memory hierarchy: the private L2 cache size has quadrupled and the SLLC, unlike all previous Intel processors, has been designed following a mostly non-inclusive policy. AMD chose similar policies since its inception, namely strict exclusion between the private cache levels, and mostly-exclusion between private cache levels and the SLLC. So we think non-inclusive content policies seem to be a consolidating trend worth focusing.

The remaining of this chapter is organized as follow. Section 2.2 describes the state of the art. Section 2.3 explains the hardware framework used in this chapter. Section 2 presents the detailed characterization. And section 2.5 summarizes the conclusion remarks.

#### 2.2 State of the Art

The characterization of a new benchmark suite is a recurrent research activity in the computer architecture community. In this section, we present the state of the art in two areas: benchmark characterization and selection of simulation intervals.

#### 2.2.1 Benchmark Characterization Methodologies

Benchmark characterization may be carried out through simulation or by using hardware counters. On the one hand, simulation provides a flexible experimentation framework that allows the evaluation of different memory hierarchy configurations, such as cache sizes or replacement policies. Unfortunately, hardware components in recent processors, such as prefetchers, can not be accurately modelled since their implementation details are not fully disclosed. Moreover, a complete benchmark simulation may require weeks or months, so studies based on simulation typically characterize only a small section of the selected benchmarks.

On the other hand, real execution is able to capture the behavior of state-of-the-art hardware components. Performance monitoring support included in commercial systems collects execution events that can be used to obtain metrics that characterize benchmark behavior during their real execution with a very low overhead. However, using real execution makes it difficult to perform design space exploration, since hardware configuration capabilities are limited.

There are many papers devoted to the SPEC CPU2006 characterization. For instance, Jaleel et al. characterize the behavior of the suite with different cache sizes on a simulator [87], Korn et al. study its performance according to page size [97].

Regarding SPEC CPU2017, we have only found two characterization studies: Limaye et al. [100] and Panda et al. [126]. They analyze the behavior of benchmarks on an Intel processor from the Haswell family. Hardware counters are used to collect the amount and type of executed instructions, memory footprint, and cache misses at all levels of the memory hierarchy. Both papers end up presenting a methodology to classify benchmarks. Regarding the characterization of the use of the memory hierarchy, they show some limitations. Namely, characterization is performed on old systems, local miss ratios are used as performance metric instead of MPKI, and the sensitivity to cache size or hardware prefetching is not studied.

With respect to the content management in shared LLCs, many processors use an inclusive policy (LLC content is a superset of all private caches), however, using instead a mostly non-inclusive policy (LLC acts as a victim cache which may, or may not, evict cache lines on hits) seems to gain momentum through more elaborated coherence protocols. AMD calls the same policy "mostly-exclusive", and started using it in its first processor with shared LLC, the 2007 4-core Opteron Barcelona [27]. All the following AMD processors, such as the 6-core Istanbul (2009), the 12-core Magny Cours (2010), the 16-core Bulldozer (2011) or, recently the 4-core Zen Core Complex (2016) evolved in cache sizes, coherency protocols and core features, but all have maintained the same mostly-exclusive contents policy. So we think characterizing benchmarks through the Intel Skylake-SP fits well with this trend.

In this work, hardware counters have been used to obtain metrics about the

execution of the benchmarks on a Skylake-SP processor. Intel's Model Specific Registers (MSR) allow us to independently enable or disable the different hardware prefetchers. The *Intel Cache Allocation Technology (CAT)* allows us to vary the LLC space occupied by an application modifying its number of allocated ways. In this way, we characterize the behavior of the entire benchmark with different hardware configurations of the memory hierarchy.

#### 2.2.2 Selection of Benchmarks and Simulation Intervals