International Federation of Automatic Control

SOFTWARE FOR

COMPUTER

CONTROL

Preprints of the 3<sup>rd</sup>

IFAC / IFIP Symposium

Madrid, Spain

5 - 8 October 1982

## **Editors**

**G. Ferraté** Barcelona, Spain

E.A. Puente Madrid, Spain.

# SOFTWARE FOR COMPUTER CONTROL

Preprints of the 3<sup>rd</sup> IFAC / IFIP Symposium.

Madrid, Spain

5 - 8 October 1982

**Editors**

G. FERRATE

Barcelona, Spain.

**E.A. PUENTE**

Madrid, Spain.

Published for the

INTERNATIONAL FEDERATION OF AUTOMATIC CONTROL

# Copyright © IFAC 1982

All Rights Reserved, No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means: electronic electrostatic, magnetic tape, mechanical, photocopying, recording or otherwise, without permission in writing from the copyright holders.

First edition 1982

## 3<sup>rd</sup> IFAC/IFIP SYMPOSIUM ON SOFTWARE FOR COMPUTER CONTROL

# Sponsored by

IF AC Technical Committee on Applications

**IFAC Technical Committee on Computers** IF AC Technical Committee on Education

# Co-Sponsored by

IFIP Technical Committee on Computer Applications in Technology

# Organized by

Comité Español de la IFAC

Departamento de Ingeniería de Sistemas y Automática de la

Universidad Politécnica de Madrid

#### International Program Committee (IPC)

G Ferraté, E (Chairman)

P. Albertos, E. A. Buzo. MEX

C.M. Doolittle, USA

P. Etzer, D.

D.G. Fisher, CDN

J. Gertler, H

R. Isermann, D

P.M. Larsen, DK

M. Mansour, CH

J.S. Meditch, USA

R. Mezencev, F

M. Novak, CS

E.A. Puente, E

V Streic, CS

B. Tamm, SU

E.A. Trakhtengerts, SU

J.D.N. Van Wyk, ZA T.J. Williams, USA

# National Organizing Committee (NOC)

E.A. Puente (Chairman)

M. Alique

R. Aracil

A.J. Avello

M. Collado

L. Basañez

E. Bautista

J.G. Bernaldo de Quirós

E.F. Camacho

J.M. Coronado R. Huber

J.A. Martin-Pereda

M. Mellado

P. de Miguel

J.A. de la Puente

R. Puigjaner

A. Rodriguez

# PROGRAMMABLE LOGIC CONTROLLERS AND PETRI NETS: A COMPARATIVE STUDY

#### M. Silva & S. Velilla

Departamento de Automática, Escuela Superior de Ingenieros Industriales.

Universidad de Zaragoza.

Abstract. In a Petri Net (PN) model of a system, a small subset of transition can usually be fired. Therefore several special Programmable Logic Controllers (PLCs) have been proposed looking for more performant simulation schemas. Some of them are general purpose microcomputer-based. Others are constructed using specialised microprocessors (microprogrammed or not).

This paper presents a conceptual framework to systematize concepts introduced in different PLCs specifically designed for safe (1-bounded) PN simulation. To compare their "conceptual" performances, basic proposed schemas (and other new ones) were programmed on a same microcomputer (M 6801). The technique used for comparison of performances consists of: (1) building different data structures to represent PN and its marking and (2) building performance models using a small set of parameters that caracterizes the complexity of PN-models.

It is shown that there is no "optimum" schema. The "best" one is a function of the net to be realised.

<u>Keywords</u>. Computer control; machine oriented languages; microprocessors; programming language; programmable logic controllers; performances; Petri nets.

#### INTRODUCTION

The advantages of programmed logic make possible the growing interest in a special class of computers for system control named Proquammable Logic Controllers (PLC). On the other hand, the complexity of modern logic control systems contributes to the increasing use of Petri Nets (PN) as a modelling tool. In this paper safe (1-bounded) PN and special PLCs are considered.

PLCs are a very simple class of computers that work cyclically (a cycle is named a <a href="Ireat-ment Cycle">Ireat-ment Cycle</a>, TC). In classical PLCs, the simulation of logical automatisms modeled with PN can be done in a very easy way: programming all transitions of the net in such a manner that every logic equation will be executed in each TC.

In a PN model of a system, only a small subset of transitions can usually be fired. Therefore, several special PtCs were proposed to make the simulation more performant.

Proposed systems vary from general purpose based computers (Silva & David, 1979; Chocrón, 1980) to <u>special</u> purpose based computers (microprogrammed as in (Daclin, 1976) or in (Tafazzoli, 1979), or not microprogrammed as in (Defrenne, 1979) or in (Silva & Velilla, 1980).

This paper focusses on the two main design problems for PN based PLCs: (1) the definition of PN simple specification languages and (2) the choice of an adequate PN internal representation (data structure) and an algorithm to interprete the data structure in a correct and efficient manner.

The choice mentioned in the last point relates directly to memory ocupation and execution time of a TC. A conceptual framework is presented (1) to systematize concepts introduced in different PLCs speciafically designed for safe PN simulation, and (2) to "compare" their respective "conceptual performances". All presented simulation schemas(and others) have been programmed on a M 6801.

It will be assumed that readers are familiar with basic PN terminology (Daclin, 1976; Peterson, 1981).

# PETRI NETS MODELS ESPECIFICATION LANGUAGE

To simplify the programming of PN models, the language should be <u>non-procedural</u> (non-algorithmic: the lexicographic order in wich the system is specified is not important).

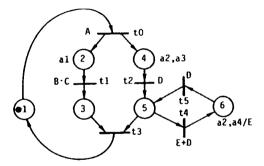

Fig. 1 A safe PN model ({A,B,C,D,E,F} are input variables and {a2,a4,a6} actions).

The main advantages of this decision are:(1) direct specification (there is not translation by the designer), (2) programming hazards be solved by the designer (they must be solved by the PLC system), (3) specification may be validated (Martinez & Silva,1982) and (4) it is very easy to give a redundant specification to avoid errors in the data in put process.

Languages may be on a "fill-in-the blank" level, or on a "higher" one. There PN model structure and interpretation may be specified separated or mixed. We will speak about two different cases.

Fill-in-the-blank and separated . The structure of the PN is specified by giving, for each transition; (1) its input and output places and (2) the associated event. The interpretation is specified by defining (1) events and (2) actions associated with places. The initial marking is defined after the structure specification.

### TABLE 1 A specification of Fig.1 PN model

STRUCTURE

t0:p1/p2,p4 \$ e0; t1:p2/p3 \$ e1;

t2:p4/p5 \$ e2; t3:p3,p5/p1;

t4:p5/p6 \$ e4; t5:p6/p5 \$ e2 \$

INITIAL MARKING p1 \$

EVENTS

e0:=A; e1:=B·C; e2:=D; e4:=E+D \$

ACTIONS

p2:a1; p4:a2,a3; p6:a2,a4/E \$

Table 1 shows a specification of the Fig.1 PN model. If it is judged interesting to make the data input process redundant, the structure should be defined place by place, giving its input and output transitions.

For the Fig.1 PN we may write (it is possible to fuse this phase with the ACTIONS phase):

p1: t3/t0; p2:t0/t1; p3: t1/t3; p4:t0/t2;

p5: t2,t5/t3,t4; p6:t4/t5 \$

"Higher level" and mixed. With this kind of languages it is possible to use symbolic names for places and transitions. The structure is usually defined transition by transition with its actions and events. Actions associated with places are defined place by place as before.

Some other important facilities to consider here are the specifications of Macroplaces, Macrotransitions, Subprograms, ... (Martinez & Silva. 1982).

From the translation point of view, the kind of language to be selected is a function of the implementation method to be used.

SOME PREVIOUS CONSIDERATIONS ABOUT IMPLEMENTATIONS.

To implement specialized on safe PN simulation PLCs, there is a wide range of freedom. That will be briefly considered. The conditions under which different realizations will be compared are also defined.

<u>PLC simulation power</u>. There are several PLC systems in wich events are only <u>a variable</u> (complemented or not) and actions are only <u>unconditionnaly</u> associated with places. At the other extreme there are PLC systems in which events and conditions may be specified by any boolean function of external and internal variables. Conditional actions can be employed.

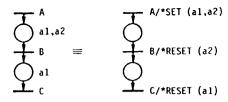

In the following paragraphs we will consider any boolean function as defining events but only inconditional actions as being associated with places and/or transitions. With this restriction, Fig. 2 shows how it is possible to consider that actions are only associated with transitions. This is a very im-

Fig. 2 Inconditional actions associated to places can be represented around transitions

portant decision for the simplification of TC, because most PLCs that permit conditional actions work in two phases: (1) marking evolution and generation of actions associated to transitions and (2) conditional action generation. Only one special PLC (Silva & David, 1979) works with conditional actions in a single nhase. It is based on a slightly more complicated but more performant simulation schema.

Computer Support. Some PLCs work on special

hardware. For example COLERES (Daclin, 1976) is constructed around a microprogramming sequen cer (INTEL 3000). Defrenne (1979) has built a special hardware using a specialized micro processor (MOTOROLA 14500 B) and external hardware. Other PLCs use general purpose microcomputers and are specialized by software only. For this type there are several differences because some systems execute, after a macroexpansion process, the code of the sup port microcomputer. At the other extreme an interpreter or simulator reads a data structure representing the PN and its interpretation.

To compare the conceptual performances of special PLCs, the basic proposed schemas will be considered by using a general purpose microcom puter with interpreters (each reading a data structure) or executing directly code (in one case, a hardware SCANNER will be added to the system).

Synchronous or non-synchronous interpretation. Most proposed PLCs take inputs when a TC star ts. This is done to avoid hazards due to va lue changes during a cycle. The evolution of some systems is defined as synchronous if PN marking evolues globally at the TC end or just before conditional action calculations. A PLC is synchronous even if there is no real time clock to start the next TC.

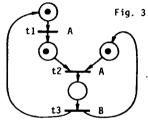

Non-synchronous simulation schema can cause problems. For example, the Fig. 3 PN simula tion will give a non-safe intermediate marking if t<sub>1</sub> is treated before t<sub>2</sub>. Also, it is interesting to note that with non-synchronous evolutions the final marking depends on the order in which transitions are considered by the interpreter. Synchronous interpretation is always longer than non-synchronous interpretation.

Internal representation. Data structure repre senting the PN may use matrices or lists.Lists may be organized in different fashions as will be seen later on.

Basic schemas will be compared in the following paragraphs.

Fig. 3 A PN model that is safe due to the interpretation.

#### MATRIX REPRESENTATION OF PETRI NETS

In this paragraph we present a data structure and a driving algorithm to simulate PN. The ba sic schema will be complicated a little more in order to obtain faster TC.

A Matrix-Based Basic Schema. PN structure will be represented by two matrices:(1) prematrix, E (n is the number of places and m the number of transitions) and (2) flow--matrix, Fnym. They are defined as:

• IF  $p_i$  is an input place of  $t_i$  THEN  $E_{ij} = 1$ ELSE  $E_{ij}^{ij} = 0$

•

$$F_{ij} = \alpha + \beta$$

, where:

$$\begin{cases} \frac{IF}{p_i} & \text{p}_i \text{ is an input place of } t_j \\ \frac{IF}{p_j} & \text{p}_i \text{ is an output place of } t_j \\ \frac{IF}{ELSE} & \alpha = 0 \end{cases}$$

Let us represent the marking by the boolean vector M<sub>px1</sub>, and let us define A<sup>1</sup> the j-th column of matrix A. With this notation it is easy to show that:

(a)

$$t_j$$

is enabled by M iff  $E^j \Rightarrow M$  (1)

(a)

$$t_j$$

is enabled by M iff  $E^j \Rightarrow M$  (1)

(b) If  $t_j$  is fired, the new marking,  $M^+$ , is:  $M^+ = M + F^j$  (2)

Now:  $[E^j \Rightarrow M] = [E^j \cdot M = E^j] = [E^j \cdot \overline{M} = 0]$  (3)

Then t, is enable iff  $E^{j} \cdot M = 0$ . Now let us define matrix  $\emptyset$  by:

IF

$$F_{i,j} \neq 0$$

THEN  $\emptyset_{i,j} = 1$  ELSE  $\emptyset_{i,j} = 0$

Since M and M are boolean, eq. (2) may be rewritten as (# = exclusive-OR):

$$M^+ = M \oplus \emptyset^j$$

or  $\overline{M}^+ = \overline{M} \oplus \emptyset^j$

In conclusion, all operations are boolean vectorized, and thus PN simulation may be performant in most general purpose microcomputers.

A faster Matrix-Based-Schema.To accelerate the simulation it is possible to think of executing iterations only for enabled tran sitions (they drive the simulation process). Since a transition may have several input places, it takes a long time to obtain the transition enabled boolean vector, 9\*.

To reduce the enabling concept to a boolean one, each transition will be "represented" by one of its input-places (Silva & David, 1979).

To enable t<sub>i</sub>, represented by p<sub>i</sub>, it is ne cessary (but not sufficient) that p<sub>i</sub> be marked. Let us define the boolean vector on x 1 as: " $\theta_i = 1$  iff the place  $(p_i)$  that represents  $t_j$  is marked [M(i)=1]".

In the above presented conditions, when a transition is fired it is very easy to obtain the new vector,  $\mathbf{e}^+$ .

Let us define the boolean matrices Amam and  $B_{mxm}$  where: (1)  $A_{i,j}=1$  iff  $t_i$  is represented by a  $t_j$  output-place. (2)  $B_{i,j}=1$  iff it is also represented by the place that represented ts ti.

When t<sub>i</sub> is fired, it is easy to see that

# e+ = 0 0 Aj 0 Bj.

To simplify calculations and reduce memory occupation we will use only matrix D, where  $D^{j}=A^{j}$   $\Theta$   $B^{j}$  and then  $\Theta$  +=  $\Theta$   $\Theta$   $D^{j}$ . Table 2 shows the new simulation algorithm.

Performances between basic and faster schemas will be shown later. The faster schema has  $\approx 50\%$  more memory occupation (matrix D and vectors  $\theta$  and  $\theta_{aux}$ ) and its execution time is  $\approx 60\%$ .

To reduce memory occupation, list representations may be used because E, F and D are usually sparse-matrices.

#### LIST-BASED REPRESENTATIONS OF PETRI NETS

The memory occupation of matrix representations is mainly proportional to nxm. With list-based representations, memory occupation will usually be linear on m and n.

<u>List-Based Basic Schema</u>. The PN structure is represented by a transition list. Each element list describes: (1) its input and output places; and (2) associated events and actions

The marking is represented by a boolean vector, M (for synchronous simulation a Maux vector may be used). Net simulation is done by considering transition by transition. The simulation algorithm is very simple, but execution time will be very important because it is necessary to test all the PN transitions. This schema has been adopted by Tafazzoli (1979) to simulate Capacity PN. He has developed a special microprogrammed computer. Some faster list-bases schemas will be considered below.

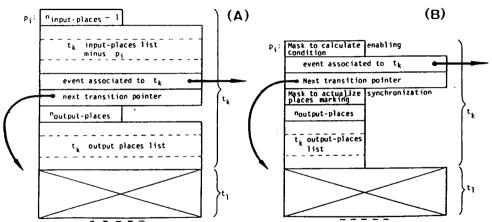

P-T List and Marking Driven Simulation schemas. To avoid the non-performant simulation schema presented in the preceding subparagraph, transitions to be tested will be restricted to those for which their representing place is marked. Figure 4a shows a data structure associated

#### TABLE 2 Control algorithm for matrix represented PN using the faster schema

with each place. It consists of a represented transition list. The data structure associated with p<sub>i</sub> will be inspected <u>only</u> if p<sub>i</sub> is marked. In this case only a subset (usually small) of transitions will be considered.

In a first schema, it is possible to assume that marked places are selected by <u>scanning</u> a marking vector. This scanning may be done:

(1) by the microprocessor (by serializing it with the selected-places treatment), or (2) by a simple SCANNER-processor (Daclin, 1976; Silva & Velilla, 1980).

An alternative to scanning techniques (Silva & David, 1979) is to use a <u>pointer</u> for each place that represents at least one transition. Each place having an output transition not represented by the place will be implemented in a marking boolean subvector (usually very small). These places will be named <u>synchronization nlaces</u>(they will be considered as software flags). To avoid redundant implementations of the marking of any place (a place may simultaneously serve the function of representation and synchronization), it is interesting to choose two disjointed subsets (PruPs=P, PrOPs= Ø).

This condition is usually verified, but when this is not so, for a given PN, then there

(Note: If next transition pointer \* 9000, there is no more transition represented by  $p_1$ )

Fig. 4 Two place-transition lists PN structure representation.

are always equivalent nets for which the condition holds (see Fig. 5).

Figure 4b shows another form to represent PN structures. The simulation algorithm takes pointers corresponding to representing marked places from a list (normally a stack) and builds the list (stack) for the next TC. When the TC ends, the rôle of the two lists is changed: the built list becomes the treatment list while the older list is forgotten and a new one will be built.

As a general comment, it is interesting to point out that partitions between representation and synchronization places allow better performances, but regularity in place representation and treatment is lost.

T-List and Enabled Transition Driven Simulation Schemas. This last schema may be viewed as an improvement of the "List Basic Schema" because only data structure associated with enabled transitions will be considered in a IC. Then as in the former schema, execution-time will be reduced.

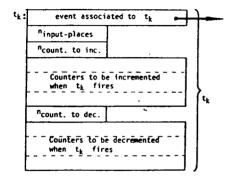

To make a performant simulation, a counter will always be associated to each transition (Chocron, 1980). This will count the number of input places that are not marked. Obvious the data structure associated to a transition. The simulation algorithm proceeds as follows:

(1) When an enabled (possibly fired) transition treatment is finished, then another one is looked for.

(2) When a transition t, is fired, then:(a) C, is set to the number of t, input places (this is correct because only safe PNs are considered);(b) counters associated with the other output transitions of the fired transition input places will be incremented (because the firing of t, in crements the number of their non-marked input places); and (c) counters associated with the output transitions of the output places of t, will be decremented.

Fig. 5 A transition list definition for representing PN structure.

As when the simulation schema is marking-driven, an enabled transition may be searched for: (1) by scanning the counter vector C; and (2) by using two lists (stacks). An important difference between the latter schema and the representing synchronization marking driven schema is that vector C can not be eliminated, because it is essential to know when a transition reaches or leaves the enabled state. "t,"—pointer, or its transition number, will be added to the enabled transition list when decrementation of  $C_j$  gives  $C_j = 0$ .

Finally, it is interesting to note that, in fact, vector C defines indirectly the marking of the PN. In the schemas defined in this subparagraph, marking does not appear directly. It will state an important problem when conditional actions are associated with places. In this case a double marking representation is normally used: (1) marking vector M; and (2) counter vector C.Obviously this redundant schema will reduce performances.

#### PERFORMANCE COMPARISON

The approach used to make performance comparison consists in building some simple evaluation models using a small set of parameters. These parameters should characterize the implementation complexity of the safe PN. The approach to the construction of the performance models is presented in (Silva, 1979). In this paper, we will only analyze results obtained for the six PLC classes studied below (the six columns in Table 3). In fact, ten different special PLSCs have been programmed on a M6801.

To avoid long formula manipulations, comparison will be made by using four test cases(in table 3 rows). The six parameters used to de fine "the complexity" of a PN are: (1) the number of places, n, and transitions,  $m_i(2)$  the mean number of input places of a transition,  $n_{it}$ , and of input transitions of a place,  $m_{ip}$ ; and (3) for a given TC, the number (a maximum estimation) of marked places,  $n_{m}$ , and of fired transitions,  $m_{e}$ .

Table 3 shows performance estimation. In this table only PN structure and marking are considered (i.e.: event calculation and action generation are not considered at all). It may be easily seen that matrix-based methods are not performant. They may be of some interest for very small PN (n<16, m<16) [memory occupation and execution-time grows mainly as  $K_1$  n,m +  $K_2$  n +  $K_3$  m +  $K_4$ ]

When comparing only list-based methods it is clear that stack-driven simulation, schemas are better, except when a hardware scanner is used. It may also be seen that, in case 2 and for data structure interpretation, the "T-list & stack" method is slightly more performant than marking-driven solutions. It should be easily understood because case 2 PN is a Marked Graph (dual of a State Machine). As a general com-

|                                                     | Data Structure                                           |                                                                                                |         | Matrix        |                       | P-T List &  |          | T List &   |  |

|-----------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|---------|---------------|-----------------------|-------------|----------|------------|--|

| Interpretation Executable Code                      |                                                          |                                                                                                | Basic   | Faster        | Scanning              | Stacks      | Scanning | Stacks     |  |

| <b>!</b>                                            |                                                          | (+Hardware Scanner)                                                                            |         |               |                       |             |          |            |  |

| 1                                                   | STATE<br>GRAPH                                           | n=23, m=32, n <sub>it</sub> =1<br>m <sub>ip</sub> =1.4, n <sub>m</sub> =3, m <sub>d</sub> =2   | 1749 —  | 1172 –        | 587<br>394<br>(104)   | 364<br>180  |          | 315        |  |

| 2                                                   | MARKED<br>GRAPH                                          | n=32, m=23, n <sub>it</sub> =1.4<br>M <sub>ip</sub> =1, n <sub>m</sub> =4, m <sub>d</sub> =1.5 | 1577    | 1030 —        | 715<br>523<br>(128)   | 356<br>187  | 425 —    | 347<br>249 |  |

| 3                                                   | PN                                                       | n=m=32, n <sub>it</sub> =1.4<br>m <sub>ip</sub> =1.4, n <sub>m</sub> =4, m <sub>d</sub> =2     | 2147 —  | 1211 -        | 832<br>533<br>(138)   | 436         |          | 487<br>333 |  |

| 4                                                   | PN                                                       | n=m=100, n <sub>it</sub> =1.4<br>m <sub>ip</sub> =1.4, n <sub>m</sub> =12, m <sub>d</sub> =6   | 17295 — | 8860 —        | 2585<br>1557<br>(362) | 1249<br>530 |          | 1339       |  |

| Comparative performances over a (1),(2) and (3) mix |                                                          | 9.45                                                                                           | 5.9     | 3.7<br>(0.64) | 2 ①                   | 2.8         | 2.26     |            |  |

| Me<br>pe                                            | Memory ocupation (bytes) per transitions in list-repres. |                                                                                                | _       | _             | 11.5                  | 26.5        | 12.0     | 10.5       |  |

TABLE 3 Execution time in machine cycles (M6801) and memory ocupation estimation

ment, it may also be stated that "usually" marking-driven simulation schemas are more performant than transition-driven ones. In this manner, when a "I-list & stack" schema is used, before every push or after every pull of a transition pointer a zero test on the corresponding counter-vector element is needed (operations will be realised only if the transition is enabled).

For list-based schemas, memory occupation is "mainly" linear with m (see Table 3,last row). At this point, it may be stated, for example, that the "P-T list & Stacks" execution code version is twice as fast than the interpreted one, but consumes about 2,65 times more memory space.

#### CONCLUSIONS

We will concentrate on the extensibility of the list-based representation principles for realising: non-safe PN, PN based self-testing, conditional actions and translation from specification language.

Transition-based presented schemas can not be extended for non-safe PN when the counter-vector is used. Self-testing techniques (usually marking-based) and conditional actions associated to places are difficult to realize because we have not a direct representation of the marking. Translation is easy.

Place-based presented schemas may be easily extended for non-safe PN and conditional actions associated to places. The stack-based method is difficult for self-testing PN-based procedures. These reasons together with perfomance results, make place-based schemas "better" in most cases. The Stack-based method needs a more complicated translation process.

Note that for list represented methods, table 3 gives performances for non-synchronous evolutions. Stack-based methods will maintain them

for synchronous evolutions, but scanning based methods will be slower. At this point, it is interesting to note that the use of microprocessors with autoincrement addressing or two stack pointers will make stack-based schemas much more performant. For that reason, the study is being partially remade by using M6809, LSI-11 or similar microprocessors.

Finally, it is important to recall that event calculations and action generation (a usually very important part of each TC) will lend considerable uniformity to the performances rendered by most of the considered methods.

#### REFERENCES

Chocron, D.(1980). Un Système de Programmation par RdP de Controleurs Industriels. Master Comp.Sc.,Montreal.

Daclin, E. & M.Blanchard (1976). Synthèse des Systèmes Logiques. Ed. Cepadues. Toulouse. pp 201-214.

Defrenne, J. & co-workers (1979). Gestion Rapide des RdP par p-P monobit. MIMI 79, Zürich, pp.62-66.

Martinez, J. & M. Silva (1982). A package for computer design of concurrent logic control systems. SOCOCO-82, Madrid.

trol systems. SOCOCO-82, Madrid.

Peterson, J.L. (1981). Petri Net Theory and the Modelling of Systems. Prentice-Hall, Englewood Cliffs, N.J.

Silva, M. & R. David (1979). Synthèse progra

Silva, M. & R. David (1979). Synthèse progra mée des automatismes logiques décrits par RdP. <u>RAIRO-Automatique</u>, vol. 13, n°4, pp 369-393.

Silva, M. (1979). Evaluation des performances des applications temps réel de type logique. MIMI 79. Zürich. pp 152-157.

logique. MIMI 79, ZUrich, pp 152-157.

Silva, M. & S. Velilla (1980). Sistema especializado en la simulación de redes de Petri Sanas. I Simp. Nacional sobre Modelado y Simulación (IFAC). Sevilla.pp 81-88.

Tafazzoli, M.E. (1979). Realisation d'un in teroreteur matériel de réseau de Pétri. Thèse 3eme. Cycle.Nice.